In the wake of TSMC’s recent Open Innovation Platform event, I spoke to Frank Ferro, Senior Director of Product Management at Rambus. His presentation on advanced memory interfaces for high-performance systems helped to shed some light on the evolution of system memory for leading edge applications. System implementers now… Read More

Tag: bandwidth

4 goals of memory resource planning in SoCs

The classical problem every MBA student studies is manufacturing resource planning (MRP II). It quickly illustrates that at the system level, good throughput is not necessarily the result of combining fast individual tasks when shared bottlenecks and order dependency are involved. Modern SoC architecture, particularly … Read More

How to handle petabyte-scale traffic growth?

If you search the web for IP traffic growth, you will find many graphics, but the common result is that IP traffic is growing with high CAGR for many years and will again continue to grow with such high CAGR for the next five years. For example the global mobile data traffic is expected to grow with 53% CAGR 2015-2020… even if the smartphone… Read More

Finding under- and over-designed NoC links

When it comes to predicting SoC performance in the early stages of development, most designers rely on simulation. For network-on-chip (NoC) design, two important factors suggest that simulation by itself may no longer be sufficient in delivering an optimized design.

The first factor is use cases. I think I’ve told the story … Read More

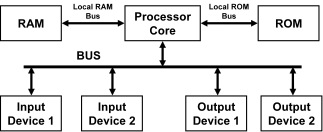

I/O Bandwidth with Tensilica Cores

It is obviously a truism that somewhere in an SoC there is something limiting a further increase in performance. One area where this is especially noticeable is when a Tensilica core is used to create a highly optimized processor for some purpose. The core performance may be boosted by a factor of 10 or even as much as 100. Once the core… Read More