The semiconductor industry is experiencing unprecedented growth in complexity as advanced process nodes, heterogeneous integration, and AI-driven workloads demand increasingly sophisticated chip designs. At the same time, semiconductor companies face rising design costs, increasing engineering workloads, and a shrinking… Read More

Tag: aprisa

Digital Implementation and AI at #62DAC

My first panel discussion at DAC 2025 was all about using AI for digital implementation, as Siemens has a digital implementation tool called Aprisa which has been augmented with AI to produce better results, faster. Panelists were from Samsung, Broadcom, MaxLinear, AWS and Siemens. In the past it could take an SoC design team… Read More

Siemens Describes its System-Level Prototyping and Planning Cockpit

We all know semiconductor design is getting harder. Much harder when you consider the demands of AI workloads and heterogeneous integration of many chiplets in a single package. This class of system demands co-optimization across the entire design flow. For example, functional verification, thermal analysis, signal and power… Read More

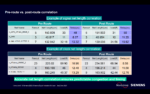

Achieving Optimal PPA at Placement and Carrying it Through to Signoff

Performance, Power and Area (PPA) metrics are the driving force in the semiconductor market and impact all electronic products that are developed. PPA tradeoff decisions are not engineering decisions, but rather business decisions made by product companies as they decide to enter target end markets. As such, the sooner a company… Read More

Designing a FinFET Test Chip for Radiation Threats

Much of the technology that goes into aerospace applications is some of the most advanced technology that exists. However, these same systems must also offer the highest level of reliability in what is arguably an extremely difficult environment. For semiconductors a major environmental risk in aerospace applications are … Read More

APR Tool Gets a Speed Boost and Uses Less RAM

Automatic Place and Route (APR) tools have been around since the 1980s for IC design teams to use, and before that routing was done manually by very patient layout designers. Initially the big IDMs had their own internal CAD groups coding APR tools in house, but eventually the commercial EDA market picked up this automation area,… Read More

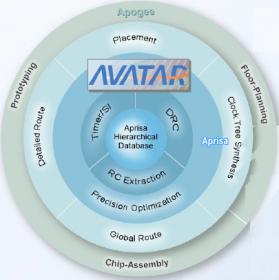

Update on Mentor’s Acquisition of Avatar Integrated Systems

Mentor Graphics, a Siemens Business, has completed their acquisition of EDA company Avatar Integrated Systems. I recently spoke with Joe Sawicki, Executive VP of the Mentor IC EDA segment, about the acquisition strategy and IC Design platform goals for integration of the Avatar products.

Avatar (formerly ATopTech) focused… Read More

Detail-Route-Centric Physical Implementation for 7nm

For many years TSMC has provided IC design implementation guidance as viewed from the process and manufacturing standpoints. The last time TSMC Reference Flow incremented, it was version 12.0 back in 2011. Since then, increased design, process and packaging related complexities of the advanced nodes have demanded more focused… Read More

Aprisa and Apogee – The New Avatars

Earlier physical optimization impacts a design QoR gain and can disclose potential hurdles in dealing with unknown design variants such as new IP inclusion or new process node issues. Along the RTL-to-GDS2 implementation continuum, a left-shift move requires a robust modeling and proper context captures in order to produce… Read More

ATopTech is Back!

One of the biggest surprises at the TSMC OIP Forum last week was the reappearance of bankrupt EDA vendor ATopTech. I spoke with former ATopTech CEO and now Avatar IS President Jue-Hsien Chern at OIP. As a survivor of several EDA legal battles myself, I understand what ATopTech went through and I am thoroughly impressed that they had… Read More