As the computing industry seeks more flexible, scalable, and open hardware architectures, RISC-V has emerged as a compelling alternative to proprietary instruction set architectures. At the forefront of this revolution stands Andes Technology, offering a comprehensive lineup of RISC-V processor solutions that go far beyond… Read More

Tag: ace

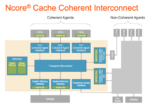

Coherency in Heterogeneous Designs

Ever wonder why coherent networks are needed beyond server design? The value of cache coherence in a multi-core or many-core server is now well understood. Software developers want to write multi-threaded programs for such systems and expect well-defined behavior when accessing common memory locations. They reasonably expect… Read More

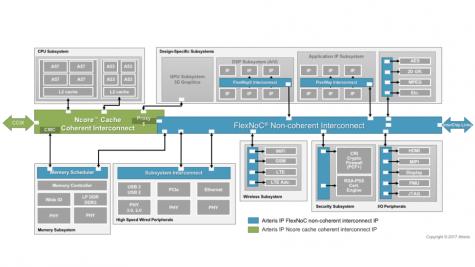

Connecting Coherence

If a CPU or CPU cluster in an SoC is the brain of an SoC, then the interconnect is the rest of the central nervous system, connecting all the other processing and IO functions to that brain. This interconnect must enable these functions to communicate with the brain, with multiple types of memory, and with each other as quickly and predictably… Read More

How Not To Be Incoherent

The advantage of working with cache memory is the great boost in performance you can get from working with a local high-speed copy of chunks of data from main memory. The downside is that you are messing with a copy; if another processor happens to be working in a similar area, there is a danger you can get out of sync when reading and writing… Read More

HLS with ARM and FPGA Technologies Boosts SoC Performance

The way SoC size and complexity are increasing; new ways of development and verification are also evolving with innovative automated tools and environment for SoC development and optimization. IP based SoC development methodology has proved to be the most efficient for large SoCs. This needs collaboration among multiple players… Read More

Taming The Interconnect In Real World For SoCs

Interconnect plays a significant role in the semiconductor design of a SoC; if not architected and handled well, it can lead to an overdesigned SoC impacting on its power, performance and area. Since a SoC generally contains multiple IPs requiring different data paths to satisfy varying latency and performance cycles, it has … Read More

Catch Mentor’s embedded sessions at ARM TechCon

For Halloween this year, why not tell your embedded software debug horror stories at ARM TechCon? Mentor will have several campfire sessions you should consider attending, but here my Halloween thread breaks down. These three sessions are all quite cheery.

This one, Software Debug on ARM Processors in Emulationis on using emulation… Read More

Analog Characterization Environment (ACE)

I’m looking forward to the 2013 TSMC Open Innovation Platform Ecosystem Forum to be held Oct. 1[SUP]st[/SUP] in San Jose. One paper in particular that has my attention is titled, “An Efficient and Accurate Sign-Off Simulation Methodology for High-Performance CMOS Image Sensors,” by Berkeley Design Automation & … Read More

Achieving Rapid Verification Convergence of ARM® AMBA® 4 ACE™ Designs using Discovery™ Verification IP

Synopsys is consolidating the company positioning on Verification IP. We have announced the launch of Discovery VIP in Semiwiki, in February this year, and we have commented about the acquisition of nSys and ExpertIO in January. This webinar, “Achieving Rapid Verification Convergence of ARM® AMBA® 4 ACE™ Designs using Discovery™… Read More