This white paper about Cadence innovative mixed-signal IP concept “Cadence Multi-Link PHY IP (SerDes, Analog Front-end, and DDR) to Design SoC Platform breaking the “Business Gap” on 14/16FF” describe the problem, the emergence of a “business gap” linked with incredibly high development cost when targeting most advanced … Read More

Tag: 10g kr

Don’t Mess with SerDes!

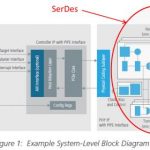

SerDes stands for Serializer/Deserializer, and SerDes is a serious piece of design, requiring an extremely experienced team of analog engineers (below 10 years’ experience, you’re still a quasi-beginner). Better to rely on an analog guru to draw the SerDes architecture and manage the team! Why does SerDes is becoming more and… Read More

Does Multiprotocol-PHY IP really boost TTM?

I have often written in Semiwiki about high speed PHY IP supporting Interface protocols (see for example this blog), the SoC cornerstone, almost as crucial as CPU, GPU or SDRAM Memory Controller. When you architect a SoC, you first select CPU(s) and/or GPU(s) to support the system basic functionality (Processor for Mobile application,… Read More

Multiprotocol 10G-KR and PCIe Gen-3 PHY IP will support big data and smartphone explosion

We have frequently said in Semiwiki how crucial is it for the SC industry to benefit from high quality PHY IP… even if, from a pure business point of view (MBA minded), PHY IP business does not look so attractive. In fact, to be able to design on-the-edge SerDes and PLL (the two key pieces), you need to build and maintain a highly skilled… Read More