Hardware-level chip security has become an important topic across the semiconductor ecosystem. Thanks to sophisticated AI-fueled attacks, the hardware root of trust and its firmware are now vulnerable. And unlike software security, an instantiated weakness cannot be patched. The implications of such vulnerabilities are vast and quite expensive to repair. How all this happened, what is known about the resultant weaknesses, how AI fits into the picture, and how to add expert-level security hardening to your existing chip design flow are all big questions to ponder.

A coherent view of the big picture with a clear path to secure chip design has been hard to find, until now. Caspia Technologies recently released a series of three short videos that explain what’s happening to chip security, why it’s happening and what can be done about it. Links to these videos are coming. You can watch all of three of them in under six minutes and your investment in time will show you why more secure chip design is so important and how to achieve it. So, let’s take a six-minute journey to secure chip design with Caspia.

Chapter 1 – The Elephant in the Room: Weak Chip Security

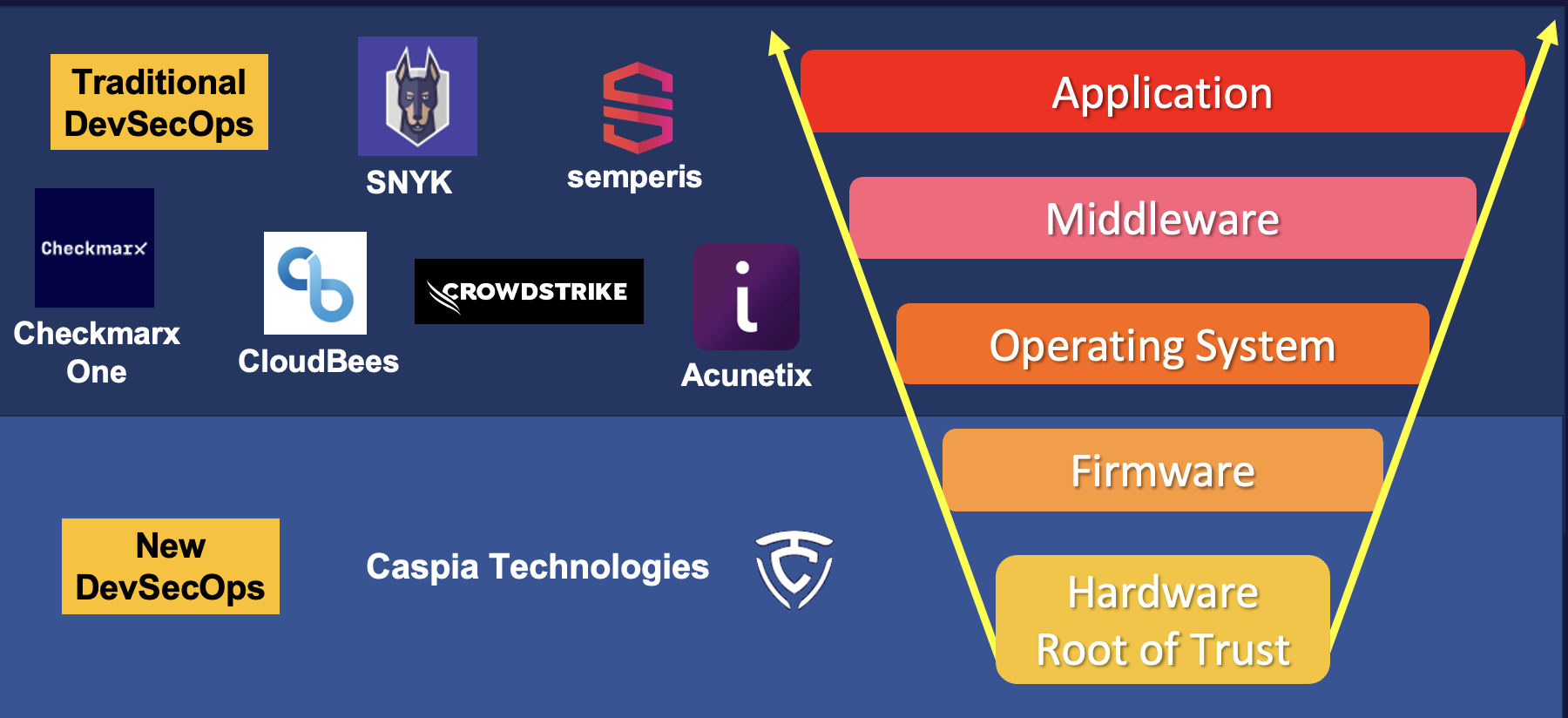

The first video frames the problem from a big-picture point of view. Why the hardware root of trust has become vulnerable and what it means for chip design are explored. The graphic at the top of this post is from this first video. What we see here is the changing landscape of DevSecOps.

For many years this high-growth industry focused on software security. Code was analyzed, weaknesses were identified, and software updates were developed and tested to increase the robustness of the code. Underlying this entire segment was the assumption that the hardware root of trust was secure and immutable. And for a long time, this was true. Some of the forces that made hardware vulnerable to attack are discussed in this segment. The result is an emerging segment of DevSecOps that focuses on fortifying the security of the hardware.

This is the sole domain of Caspia Technologies.

Chapter 2 – Identify Security Threats Before They Harm You

The second video takes a deeper dive into the chip security problem. Specific examples of hardware weaknesses and the resultant impact are taken from recent headlines. The applications cited will be familiar to all. Security risks are closer to home than you may realize.

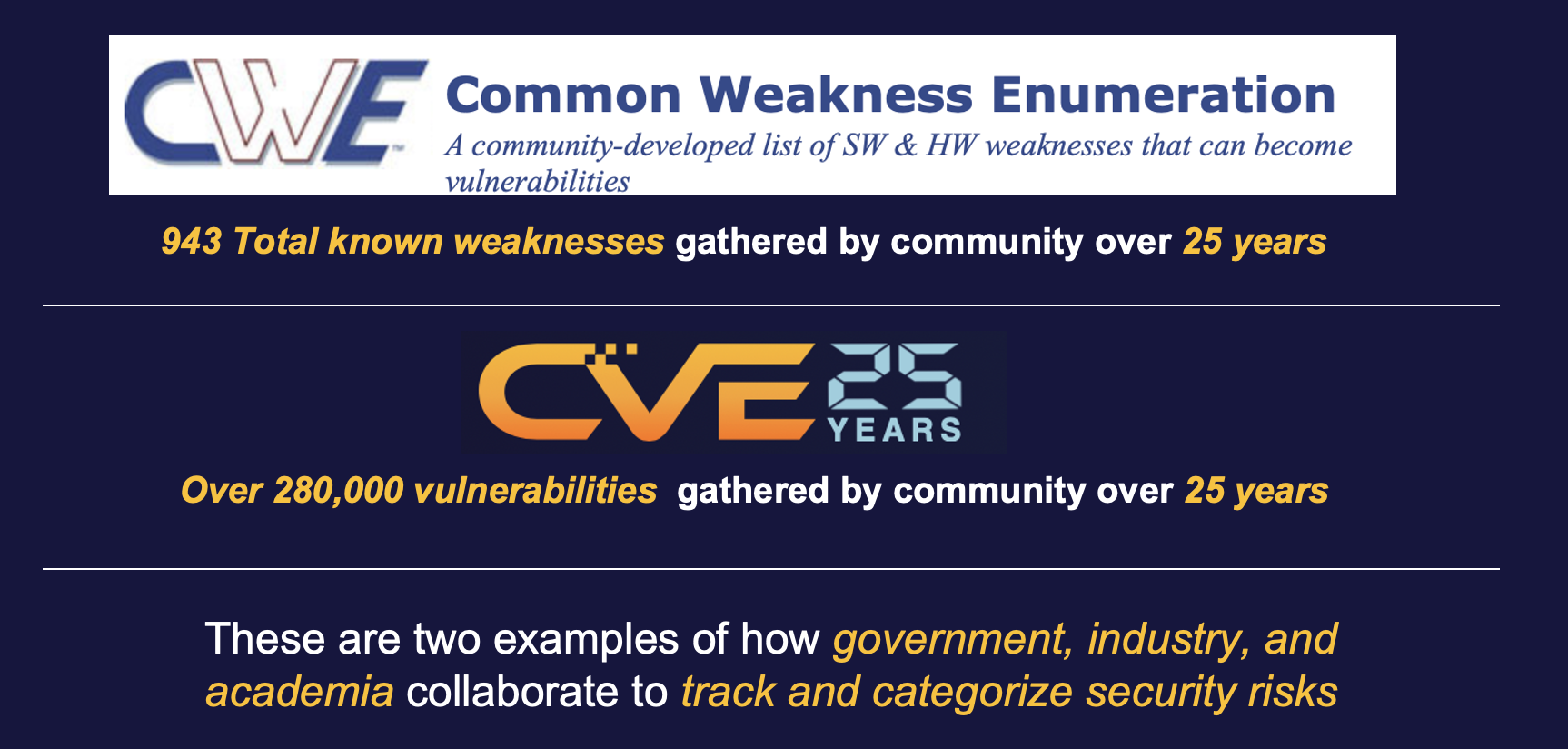

This video also showcases the substantial progress being made across the semiconductor ecosystem to understand these new security risks. Two examples of how government, industry, and academia collaborate to track and categorize security risks are presented. These efforts form the foundation for finding and fixing security risks. The diagram below illustrates some of the details discussed.

Caspia Technologies and its founding team at the University of Florida in Gainesville have been pioneering catalysts for this work. The details of these efforts and its impact are also touched on.

Chapter 3 – How GenAI Adds Expert Security to Existing Design Flows

In this final installment, approaches to apply GenAI technology in novel ways to create breakthrough security verification are presented. This video explains how GenAI capabilities can be harnessed to deliver expert level security verification to existing design teams and flows. The graphic below summarizes some of the relevant qualities that pave the way to new approaches.

The specific ways Caspia Technologies uses GenAI are detailed, with examples of how Caspia’s AI agents work together to ensure new chip designs are robust and secure against a growing threat profile.

This is the future of chip design.

To Learn More

If chip-level security is a concern (and it should be), I highly recommend investing six minutes to allow Caspia to show you the path to a more secure future. The insights are valuable and actionable.

Here is where you can view each chapter of the story:

You can also find out more about Caspia and its impact on the industry on SemiWiki here. And that’s a six-minute journey to secure chip design with Caspia.

Also Read:

Large Language Models: A New Frontier for SoC Security on DACtv

Caspia Focuses Security Requirements at DAC

CEO Interview with Richard Hegberg of Caspia Technologies

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.