By Vikash Kumar, Senior Verification Architect | Arm | IEEE Senior Member.

The Problem Every Verification Engineer Recognizes

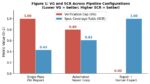

You ask an LLM to generate a UVM testbench. It produces 25 files. Everything compiles. You run the simulation — and nothing happens. The scoreboard reports zero checks. The slave driver stops after 10… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center