Power densities on chips increased from 50-100 W/cm2 in 2010 to 200 W/cm2 in 2020, creating a significant challenge in removing and spreading heat to ensure reliable chip operation. The DAC 2025 panel discussion on new cooling strategies for future computing featured experts from NVIDIA Research, Cadence, ESL/EPFL, the University… Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read MoreDAC News – proteanTecs Unlocks AI Hardware Growth with Runtime Monitoring

As AI models grow exponentially, the infrastructure supporting them is struggling under the pressure. At DAC, one company stood out with a solution that doesn’t just monitor chips, it empowers them to adapt in real time to these new workload requirements.

Unlike traditional telemetry or post-silicon debug tools, proteanTecs… Read More

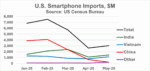

U.S. Imports Shifting

Our Semiconductor Intelligence June Newsletter showed how U.S. imports of smartphones have been on a downward trend since January 2025, led by China. Other key electronic products have also experienced sharp drops in U.S. imports from China.F

U.S. smartphone imports in May 2025 were $3.03 billion, up slightly from April but … Read More

Godfather of AI: I Tried to Warn Them But We’ve Already Lost Control!

Geoffrey Hinton, dubbed the “Godfather of AI,” joins Steven Bartlett on “The Diary of a CEO” podcast to discuss his pioneering work in neural networks and his growing concerns about AI’s dangers. Hinton, a Nobel Prize-winning computer scientist, explains how he advocated for brain-inspired… Read More

Sophisticated soundscapes usher in cache-coherent multicore DSP

Digital audio processing is evolving into an art form, particularly in high-end applications such as automotive, cinema, and home theater. Innovation is moving beyond spatial audio technologies to concepts such as environmental correction and spatial confinement. These sophisticated soundscapes are driving a sudden increase… Read More

A Quick Look at Agentic/Generative AI in Software Engineering

Agentic methods are hot right now since single LLM models seem limited to point tool applications. Each such application is impressive but still a single step in the more complex chain of reasoning tasks we want to automate, where agentic methods should shine. I have been hearing that software engineering (SWE) teams are advancing… Read More

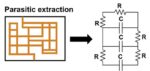

Improve Precision of Parasitic Extraction for Digital Designs

By Mark Tawfik

Parasitic extraction is essential in integrated circuit (IC) design, as it identifies unintended resistances, capacitances, and inductances that can impact circuit performance. These parasitic elements arise from the layout and interconnects of the circuit and can affect signal integrity, power consumption,… Read More

Perforce at DAC, Unifying Software and Silicon Across the Ecosystem

As the new name reflects, chip and system design were a major focus at DAC. So was the role of AI to enable those activities. But getting an AI-enabled design flow to work effectively across chip, subsystem and system-level design presents many significant challenges. One important one is effectively managing the vast amount of… Read More

Double SoC prototyping performance with S2C’s VP1902-based S8-100

As AI, HPC, and networking applications demand ever-higher compute and bandwidth, SoC complexity continues to grow. Traditional 50M ASIC equivalent gate FPGA prototyping systems have become less effective for full-chip verification at scale. Addressing this challenge, S2C introduced the Prodigy S8-100 Logic system, powered… Read More

Alphawave Semi and the AI Era: A Technology Leadership Overview

The explosion of artificial intelligence (AI) is transforming the data center landscape, pushing the boundaries of compute, connectivity, and memory technologies. The exponential growth in AI workloads—training large language models (LLMs), deploying real-time inference, and scaling distributed applications—has … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry