In engineering development, automated code generation as a pair programming assistant is high on the list of targets for GenAI applications. For hardware design obvious targets would be to autogenerate custom RTL functions or variants on standard functions, or to complete RTL snippets as an aid to human-driven code generation.… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreIntel’s IPU E2200: Redefining Data Center Infrastructure

We are in the midst of one of the most transformative periods for data center infrastructure. The explosion of AI, cloud-scale workloads, and hyperscale networking is forcing rapid innovation not only in compute and storage, but in the very fabric that connects them. At the recent Hot Chips conference, Pat Fleming gave a talk on… Read More

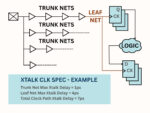

Static Timing Analysis Signoff – A comprehensive and Robust Approach

By Zameer Mohammed

Once a chip is taped out, changes in design are not possible – Silicon is unforgiving, does not allow postproduction modifications. In contrast, software can be updated after release, but chips remain fixed. Static Timing Analysis (STA) signoff serves as a crucial safeguard against silicon failures.

In modern… Read More

Beyond Traditional OOO: A Time-Based, Slice-Based Approach to High-Performance RISC-V CPUs

For decades, high-performance CPU design has been dominated by traditional out-of-order (OOO) execution architectures. Giants like Intel, Arm, and AMD have refined this approach into an industry standard—balancing performance and complexity through increasingly sophisticated schedulers, speculation, and runtime … Read More

eBook on Mastering AI Chip Complexity: Pathways to First-Pass Silicon Success

The rapid evolution of artificial intelligence (AI) is transforming industries, from autonomous vehicles to data centers, demanding unprecedented computational power and efficiency. As highlighted in Synopsys’ guide, the global AI chip market is projected to reach $383 billion by 2032, growing at a 38% CAGR. This … Read More

Orchestrating IC verification: Harmonize complexity for faster time-to-market

By Marko Suominen and Slava Zhuchenya of Siemens Digital Industries Software.

It’s often said that an orchestra without a conductor is just a collection of talented individuals making noise. The conductor’s role is to transform that potential cacophony into a unified, beautiful symphony. The same concept holds… Read More

Basilisk at Hot Chips 2025 Presented Ominous Challenge to IP/EDA Status Quo

At Hot Chips 2025, Philippe Sauter of ETH Zürich presented Basilisk, a project that may redefine what’s possible with open-source hardware. Basilisk is a 34 mm² RISC-V SoC fabricated at IHP Microelectronics on its open-source 130nm BiCMOS process in Germany. Basilisk, named after the Greco-Roman mythical creature known… Read More

How AI Workloads Shape Hardware Architecture

The evolution of AI workloads has profoundly influenced hardware design, shifting from single-GPU systems to massive rack-based clusters optimized for parallelism and efficiency. As outlined in this Hot Chips 2025 tutorial, this transformation began with foundational models like AlexNet in 2012 and continues with today’s… Read More

Advancements in High-Density Front- and Backside Wafer Connectivity: Paving the Way for CMOS 2.0

In the rapidly evolving semiconductor landscape, imec’s recent breakthroughs in wafer-to-wafer hybrid bonding and backside technologies are reshaping the future of compute systems. As detailed in their article, these innovations transition CMOS 2.0 from a conceptual framework to practical reality, enabling denser,… Read More

Podcast EP305: On Overview of imec’s XTCO Program with Dr. Julien Ryckaert

Dan is joined by Dr. Julien Ryckaert who joined imec as a mixed-signal designer in 2000, specializing in RF transceivers, ultra-low power circuit techniques, and analog-to-digital converters. In 2010, he joined imec’s process technology division in charge of design enablement for 3DIC technology. Since 2013, he oversees… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center