One technical topic I always find intriguing is the availability of links between documentation and chip design. It used to be simple: there weren’t any. Architects wrote a specification (spec) in text, in Word if they had PCs, or using “troff” or a similar format if they were limited to Unix platforms. Then the hardware designers… Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More RISC-V Now! — Where Specification Meets Scale!In forty plus years as a semiconductor professional…Read More

RISC-V Now! — Where Specification Meets Scale!In forty plus years as a semiconductor professional…Read MoreFD-SOI: A Cyber-Resilient Substrate for Secure Automotive Electronics

The paper highlights how Fully Depleted Silicon-On-Insulator (FD-SOI) technology provides a robust defense against Laser Fault Injection (LFI), a precise, laboratory-grade attack method that can compromise cryptographic and safety-critical hardware. As vehicles become increasingly digital and connected, with dozens… Read More

Podcast EP312: Approaches to Advance the Use of Non-Volatile Embedded Memory with Dave Eggleston

Daniel is joined by Dave Eggleston is senior business development manager at Microchip with a focus on licensing SST SuperFlash technology. Dave’s extensive background in Flash, MRAM, RRAM, and storage is built on 30+ years of industry experience. This includes serving as VP of Embedded Memory at GLOBALFOUNDRIES, CEO… Read More

Learning from In-House Datasets

At a DAC Accellera panel this year there was some discussion on cross-company collaboration in training. The theory is that more collaboration would mean a larger training set and therefore higher accuracy in GenAI (for example in RTL generation). But semiconductor companies are very protective of their data and reports of copyrighted… Read More

Liberty IP Excellence: Building a Robust Verification Framework for Automotive IPs

As 2025 draws to a close, the semiconductor industry continues to push boundaries, particularly in automotive applications where reliability is non-negotiable. At the TSMC Open Innovation Platform forum this year, a collaborative presentation by NXP Semiconductors and Siemens EDA stood out: “Liberty IP Excellence:… Read More

ASU Silvaco Device TCAD Workshop: From Fundamentals to Applications

The ASU-Silvaco Device Technology Computer-Aided Design Workshop is a pivotal educational and professional development event designed to bridge the gap between theoretical semiconductor physics and practical device engineering. Hosted by Arizona State University in collaboration with Silvaco, a leading provider of … Read More

PDF Solutions Calls for a Revolution in Semiconductor Collaboration at SEMICON West

SEMICON West was held in Phoenix, Arizona on October 7-9. This premier event brings the incredibly diverse global electronics supply chain together to address the semiconductor ecosystem’s greatest opportunities and challenges. The event’s tagline this year is:

Stronger Together — Shaping a Sustainable Future in Talent,… Read More

The AI PC: A New Category Poised to Reignite the PC Market

The PC industry is entering its most significant transformation since the debut of the IBM PC in 1981. That original beige box ushered in a new era of productivity, reshaping how corporations and individuals worked, communicated, and created. More than four decades later, the AI PC is emerging as a new category — one that promises… Read More

The Rise, Fall, and Rebirth of In-Circuit Emulation: Real-World Case Studies (Part 2 of 2)

Recently, I had the opportunity to speak with Synopsys’ distinguished experts in speed adapters and in-circuit emulation (ICE). Many who know my professional background see me as an advocate for virtual, transactor-based emulation, hence I was genuinely surprised to discover the impressive results achieved by today’s speed… Read More

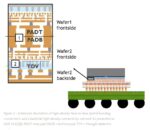

CMOS 2.0 is Advancing Semiconductor Scaling

In the rapidly evolving landscape of semiconductor technology, imec’s recent breakthroughs in wafer-to-wafer hybrid bonding and backside connectivity are paving the way for CMOS 2.0, a paradigm shift in chip design. Introduced in 2024, CMOS 2.0 addresses the limitations of traditional CMOS scaling by partitioning… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center