The PC industry is entering its most significant transformation since the debut of the IBM PC in 1981. That original beige box ushered in a new era of productivity, reshaping how corporations and individuals worked, communicated, and created. More than four decades later, the AI PC is emerging as a new category — one that promises… Read More

AI-Driven Automation in Semiconductor Design: The Fuse EDA AI AgentThe semiconductor industry is experiencing unprecedented growth in…Read More

AI-Driven Automation in Semiconductor Design: The Fuse EDA AI AgentThe semiconductor industry is experiencing unprecedented growth in…Read More TSMC Technology Symposium 2026: Advancing the Future of Semiconductor InnovationOne of my favorite times of the year…Read More

TSMC Technology Symposium 2026: Advancing the Future of Semiconductor InnovationOne of my favorite times of the year…Read More Synopsys Explores AI/ML Impact on Mask Synthesis at SPIE 2026The SPIE Advanced Lithography + Patterning Symposium recently…Read More

Synopsys Explores AI/ML Impact on Mask Synthesis at SPIE 2026The SPIE Advanced Lithography + Patterning Symposium recently…Read More Unraveling Dose Reduction in Metal Oxide Resists via Post-Exposure Bake EnvironmentIn the realm of extreme ultraviolet (EUV) lithography,…Read More

Unraveling Dose Reduction in Metal Oxide Resists via Post-Exposure Bake EnvironmentIn the realm of extreme ultraviolet (EUV) lithography,…Read MoreThe Rise, Fall, and Rebirth of In-Circuit Emulation: Real-World Case Studies (Part 2 of 2)

Recently, I had the opportunity to speak with Synopsys’ distinguished experts in speed adapters and in-circuit emulation (ICE). Many who know my professional background see me as an advocate for virtual, transactor-based emulation, hence I was genuinely surprised to discover the impressive results achieved by today’s speed… Read More

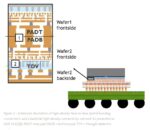

CMOS 2.0 is Advancing Semiconductor Scaling

In the rapidly evolving landscape of semiconductor technology, imec’s recent breakthroughs in wafer-to-wafer hybrid bonding and backside connectivity are paving the way for CMOS 2.0, a paradigm shift in chip design. Introduced in 2024, CMOS 2.0 addresses the limitations of traditional CMOS scaling by partitioning… Read More

Podcast EP311: An Overview of how Keysom Optimizes Embedded Applications with Dr. Luca TESTA

Daniel is joined by Luca TESTA, the COO and co-founder of Keysom. After studying microelectronics in Italy, Luca obtained his PhD in France while working with STMicroelectronics on analog/RF circuit design.

Dan explores the charter and focus of Keysom with Luca. Luca describes how Keysom is providing an automated and reliable… Read More

CEO Interview with Dr. Bernie Malouin Founder of JetCool and VP of Flex Liquid Cooling

Bernie Malouin is a technical professional with demonstrated experience from concept studies through system deployment. He has a strong track record working in dynamic environments, from highly complex, multi-million dollar development programs to deeply technical research projects. He founded JetCool Technologies … Read More

Webinar – The Path to Smaller, Denser, and Faster with CPX, Samtec’s Co-Packaged Copper and Optics

For markets such as data center, high-performance computing, networking and AI accelerators the battle cry is often “copper is dead”. The tremendous demands for performance and power efficiency often lead to this conclusion. As is the case with many technology topics, things are not always the way they seem. It turns out a lot … Read More

Webinar – IP Design Considerations for Real-Time Edge AI Systems

It is well-known that semiconductor growth is driven by AI. That simple statement breaks down into many complex use cases, each with its own requirements and challenges. A webinar will be presented by Synopsys on October 23 that focuses on the specific requirements for one of the most popular use cases – AI at the edge. The speaker… Read More

WEBINAR: Design and Stability Analysis of GaN Power Amplifiers using Advanced Simulation Tools

Why should high frequency circuit designers consider stability early in the design process? Isn’t there enough to worry about just making the circuit function at the fundamental frequency?

In the past, Microwave Engineers used to solve stability problems in the lab, perhaps adding bypassing or loss in a strategic location to… Read More

Visualizing hidden parasitic effects in advanced IC design

By Omar Elabd

As semiconductor designs move below 7 nm, parasitic effects—resistance, capacitance and inductance—become major threats to IC performance and reliability, often hiding where netlist reviews cannot reach. Design teams need advanced visualization tools like heat maps, layer-based analysis and direct layout… Read More

Statically Verifying RTL Connectivity with Synopsys

Many years ago, not long after we first launched SpyGlass, I was looking around for new areas where we could apply static verification methods and was fortunate to meet Ralph Marlett, a guy (now friend) with extensive experience in DFT. Ralph joined us and went on to build the very capable SpyGlass DFT app. So capable that SpyGlass… Read More

![[white paper] Parasitic Analysis Figures](https://semiwiki.com/wp-content/uploads/2025/10/Fig1-net-level-visualization-150x127.jpg)

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?