Discussions of chiplets has been on the rise, ever since the slowdown of Moore’s law benefits. Gartner Research projects semiconductor revenue from systems using chiplets to grow from $3.3 billion in 2020, to $50.5 billion in 2024. With any market opportunity, there are always challenges to overcome in order to realize the full… Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More

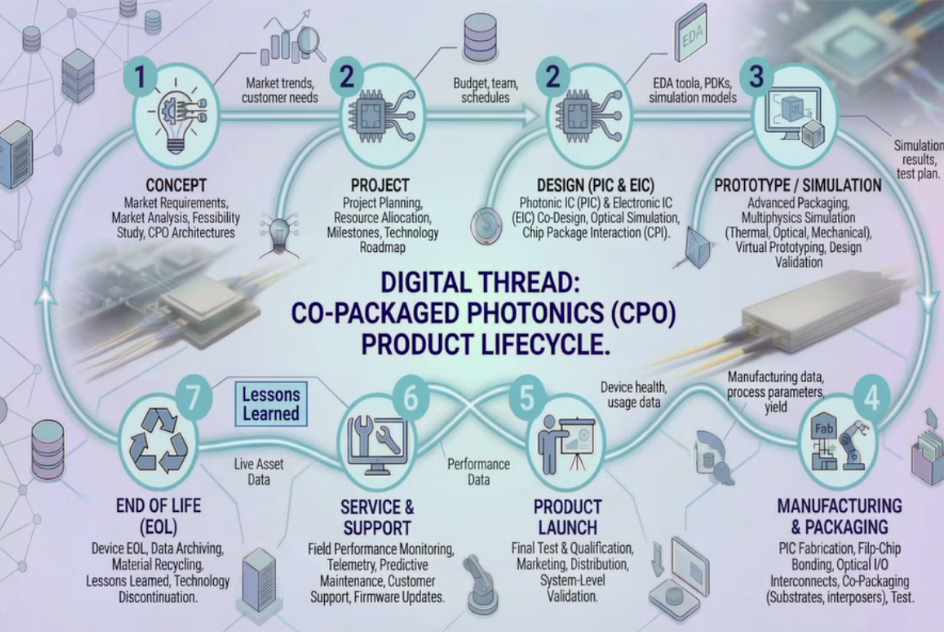

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More

yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More

RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read MoreSemiconductor Growth Moderating

The global semiconductor market in 2021 was $555.9 billion, according to WSTS data released by the Semiconductor Industry Association (SIA). 2021 increased 26.2% from 2020, the largest annual increase since 31.8% in 2010, eleven years ago. We at Semiconductor Intelligence track publicly available semiconductor market forecasts… Read More

Podcast EP62: Exploring the VSORA architecture

Dan is joined by Jan Pantzar, VP sales and marketing of VSORA, a provider of high-performance silicon intellectual property (IP) and chip solutions for artificial intelligence, digital communications and advanced driver-assistance systems (ADAS) applications based in France.

Dan and Jan explore the VSORA architecture… Read More

Dynamic Coherence Verification. Innovation in Verification

We know about formal methods for cache coherence state machines. What sorts of tests are possible using dynamic coherence verification? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO) and I continue our series on research ideas. As always, feedback welcome.… Read More

Intel buys Tower – Best way to become foundry is to buy one

-Intel jumpstarts foundry model with Tower semi buy @$54B Gets complementary tech to round out offerings

-Approval based on satisfying China’s needs as well

-Margin concerns overblown- Will it be allowed to flourish?

Intel pays up to get foundry and technology….

Intel announced a $5.4B acquisition of Tower Semiconductor… Read More

The Intel Foundry Ecosystem Explained

Exciting times for the semiconductor industry! Last week Intel announced a billion dollar fund to build a foundry ecosystem and today Intel announced they are acquiring foundry Tower Semiconductor for $5.6 billion dollars, WOW! Some people doubted Intel’s commitment to the foundry market this time. I think we can now put that… Read More

Intel Embraces the RISC-V Ecosystem: Implications as the Other Shoe Drops

On Monday, February 7, 2022, Intel Foundry Services (IFS), made a series of major announcements regarding the RISC-V architecture and ecosystem:

- Intel will be joining the RISC-V International association with a Premier Membership, and Bob Brennan, Vice President of Customer Solutions Engineering for Intel Foundry Services,

The Rising Tide of Semiconductor Cost

It Isn’t Transistory

There’s a quiet upheaval happening in the semiconductor industry. The rules that have always governed the industry are fraying, undoing assumptions that we took for granted, that was pounded into us in school. The irreproachable Moore’s Law, that exponential progress will make things cheaper, better,… Read More

Podcast EP61: A deep dive on Intel and semiconductors with Stacy Rasgon

Dan is again joined by Stacy Rasgon, Managing Director and Senior Analyst, U.S. Semiconductors at Bernstein Research. Stacy is an unusual semiconductor analyst as he holds a Ph.D. in chemical engineering from MIT. His substantial technical knowledge allows for a deep dive on Intel and other semiconductor topics that you will… Read More

Verific Sharpening the Saw

Verific is an unusual company. They are completely dominant in what they do – providing parsers for Verilog/SV, VHDL and UPF. Yet they have no ambition to expand beyond that goal. Instead, per Michiel Ligthart (President and COO), they continue to “sharpen the saw”. This is an expression I learned in sales training, habit #7 from… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea