As heterogeneous multi-die design becomes more prevalent, the focus on advanced analysis has predictably shifted in that direction. While these challenges are important to overcome, we shouldn’t lose sight of how complete systems are built. Short and long reach communication channels, system-level power management and … Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreAccelerating Advanced FPGA-Based SoC Prototyping With S2C

Having spent a significant amount of my career in EDA and IP I can tell you first hand how important picking the right prototyping partner is. I have known S2C since my interview with CEO Toshio Nakama in 2017. It has been a pleasure working with them and I look forward to seeing an S2C update at DVCon the first week of March here in Silicon… Read More

CEO Interview with Moshe Tanach of NeuReality

Moshe Tanach is co-founder and CEO of NeuReality. Prior to founding the company, he held senior engineering leadership roles at Marvell and Intel, where he led complex wireless and networking products from architecture through mass production. He also served as AVP of R&D at DesignArt Networks (later acquired by Qualcomm),

Podcast EP327: Third Quarter 2025 Electronic Design Market Data Report Overview and More with Dr. Walden Rhines

Daniel is joined by Wally Rhines, CEO of Silvaco, about the Electronic Design Market Data report that was just released. Wally is the industry coordinator for the EDA data collection program called EDMD. SEMI and the Electronic System Design Alliance collect data from almost all of the electronic design automation companies … Read More

Verification Futures with Bronco AI Agents for DV Debug

Verification has become the dominant bottleneck in modern chip design. As much as 70% of the overall design cycle is now spent on verification, a figure driven upward by increasing design complexity, compressed schedules, and a chronic shortage of design verification (DV) engineering bandwidth. Modern chips generate thousands… Read More

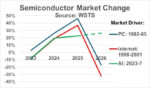

AI Bubble?

The currently strong semiconductor market is being driven by AI applications. A McKinsey survey showed 88% of businesses used AI in 2025 compared to just 55% in 2023. According to Inc.com, 306 of the S&P 500 companies mentioned AI in their third quarter 2025 earnings conference calls, up from only 53 citations three years earlier… Read More

There is more to prototyping than just FPGA: See how S2C accelerates SoC Bring-Up with high productivity toolchain?

System-on-Chip designs continue to grow in scale and interface diversity, placing greater demands on prototype capacity, interconnect planning, and bring-up efficiency. These challenges arise not only in large multi-FPGA programs but also in smaller designs implemented on a single device or a small FPGA cluster. In all cases,… Read More

Last Call: Why Your Real‑World Lessons Belong in DAC 2026’s Engineering

By Frank Schirrmeister, Synopsys

Disclaimer: This article is written in my role as Engineering Track Chair for DAC 2026

If you’ve ever walked out of DAC with a handful of practical ideas you could put to work when you return to work, you already know the value of the Engineering Track. It’s where practitioners talk to practitioners… Read More

2026 Outlook with Randy Caplan of Silicon Creations

Randy Caplan is co-founder and CEO of Silicon Creations, and a lifelong technology enthusiast. For almost two decades, he has helped grow Silicon Creations into a leading mixed-signal semiconductor IP company with 500+ customers spanning almost every major market segment. He has driven the development of key technologies … Read More

Where is Quantum Error Correction Headed Next?

I have written earlier in this series that quantum error correction (QEC), a concept parallel to ECC in classical computing, is a gating factor for production quantum computing (QC). Errors in QC accumulate much faster than in classical systems, requiring QEC methods that can fix errors fast enough to permit production applications.… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era