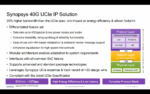

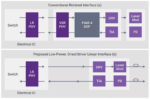

As the demand for higher performance computing solutions grows, so does the need for faster, more efficient data communication between components in complex multi-die system-on-chip (SoC) designs. In response to these needs, Synopsys has introduced the world’s fastest UCIe-based IP solution, capable of operating at a groundbreaking… Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More yieldHUB Expands Its Impact with New Technology and a New WebsiteyieldHUB is a unique company that focuses on…Read More

yieldHUB Expands Its Impact with New Technology and a New WebsiteyieldHUB is a unique company that focuses on…Read More Architecting Intelligence: The Rise of RISC-V CPUs in Agentic AI InfrastructureSiFive’s newly announced $400 million Series G financing…Read More

Architecting Intelligence: The Rise of RISC-V CPUs in Agentic AI InfrastructureSiFive’s newly announced $400 million Series G financing…Read More Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed SeaIntel, Musk, and the Tweet That Launched a…Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed SeaIntel, Musk, and the Tweet That Launched a…Read MorePQShield Builds the First-Ever Post-Quantum Cryptography Chip

Quantum computing promises to deliver vast increases in processing power. The technology exploits the properties of quantum mechanics to create revolutionary increases in performance. Medical and material science research are examples of fields that will see dramatic improvement when production-worthy quantum computers… Read More

Podcast EP248: The Far-Reaching Impact of Finwave Technology With Dr. Pierre-Yves Lesaicherre

Dan is joined by Dr. Pierre-Yves Lesaicherre. Before joining Finwave as CEO, Dr. Lesaicherre was the president, CEO and a director of Nanometrics , a leading provider of advanced process control metrology and software analytics. He also held the CEO position for Lumileds, an integrated manufacturer of LED components and automotive… Read More

CEO Interview: Adam Khan of Diamond Quanta

Adam Khan is a pioneer in diamond semiconductor technology, renowned for his foresight and expertise. As the founder of AKHAN Semiconductor, he played a crucial role in innovating lab-grown diamond thin-films for various applications, such as enhancing smartphone screens and lenses with Miraj Diamond Glass® and improving… Read More

TSMC OIP Ecosystem Forum Preview 2024

The 2024 live conferences have been well attended thus far and there are many more to come. The next big event in Silicon Valley is the TSMC Global OIP Ecosystem Forum on September 25th at the Santa Clara Convention Center. I expect a big crowd filled with both customers and partners.

This is the 16th year of OIP and it has been an honor… Read More

Linear pluggable optics target data center energy savings

Data center density continues growing, driving interconnect technology to meet new challenges. Two of the largest are signal integrity and power consumption. Optical interconnects can solve many signal integrity issues posed by copper cabling and offer support for higher frequencies and bandwidths. Still, through sheer… Read More

Smarter, Faster LVS using Calibre nmLVS Recon

Back in the 1970s we did Layout Versus Schematic (LVS) checks manually, so when internal EDA tools arrived in the 1980s it was a huge time saver to use LVS in finding the differences between layout and schematics. One premise before running LVS is that both layout and schematics are complete and ready for comparisons. Fast forward… Read More

Bird’s Eye View Magic: Cadence Tensilica Product Group Pulls Back the Curtain

Even for experienced technologists some technologies can seem almost indistinguishable from magic. One example is the bird’s eye camera view available on your car’s infotainment screen. This view appears to be taken from a camera hovering tens of feet above your car. As an aid to parallel parking, it’s a brilliant invention; … Read More

Serving their AI Masters

The Impact of the AI Revolution on the Server Manufacturers

While some will designate my research as market research, I view it differently. Having done and bought plenty of market sizing research, I have not seen it lead to any change in behaviour or strategy. It has been used to confirm a strategy already decided and the “great” … Read More

Siemens EDA Offers a Comprehensive Guide to PCIe® Transport Security

It is well-known that there is more data being generated all the time. The need to store and process that data with less power and higher throughput dominates design considerations for virtually all systems. There is another dimension to the problem – ensuring the data is secure as all this movement and processing occurs. Within… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea