The importance of semiconductors has been elevated to a national security level, and countries around the world, including Europe and the United States, are scrambling to subsidize the development of the semiconductor industry. Yang Ruilin, research director of the International Institute of Obstetrics and Mechanics of the Industrial Research Institute, believes that Taiwan's semiconductor industry is expected to lead until 2032. In terms of next-generation semiconductor technology, Taiwan must cooperate with international companies and strengthen research and development security.

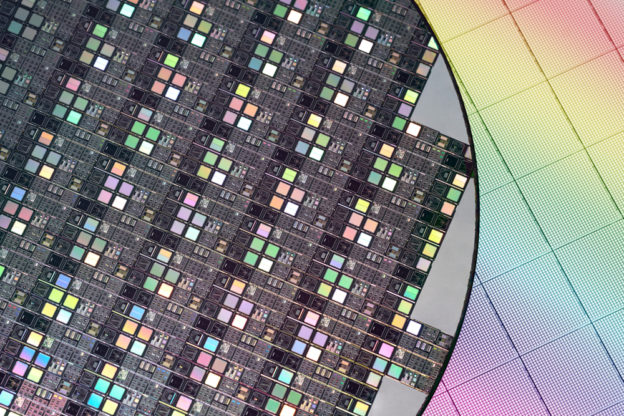

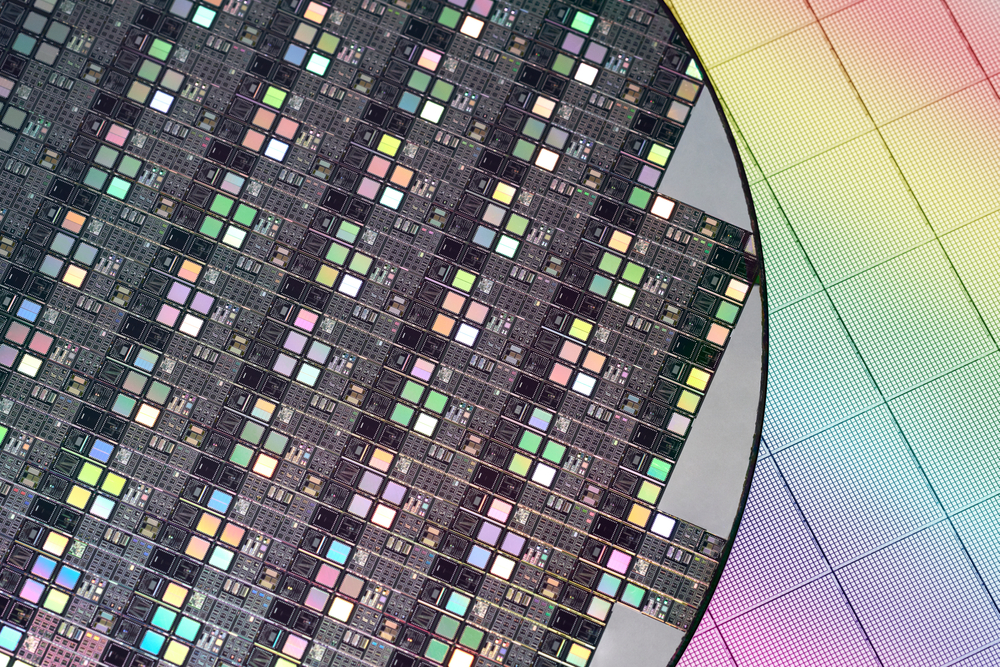

Yang Ruilin said that as geopolitical factors continue to spread, how long Taiwan's semiconductor industry can maintain its competitiveness has attracted much attention from all walks of life. TSMC will mass-produce the 2-nanometer process next year. It is estimated that before the 9-nanometer process technology, both TSMC and Taiwan Semiconductor will maintain their leading position until about 2032.

The next generation of semiconductor technology will have a new chip architecture, and will be deployed in Europe and the United States. Yang Ruilin said that China will also strive to make breakthroughs and achieve independence; Taiwan should cooperate with international cooperation in the future, and in the process, strengthen research and development security and incorporate relevant security mechanisms into the ecosystem.

The "Center for Science, Democracy and Society (DSET)" of the National Science Council today held the annual forum "Taiwan under the Geopolitics of Science and Technology" and invited Yang Ruilin, Global Marketing Director and Taiwan Director of the International Semiconductor Industry Association (SEMI) Cao Shilun, and National Taiwan University Keynote Speakers Yang Guanglei, a visiting professor at the School of Science and Technology, and Xu Zunci, director of the Taiwan Association of Southeast Asian Nations Research Center at the China Economic Research Institute, jointly discussed Taiwan's semiconductor industry and economic security under the geopolitics of technology.

Yang Guanglei reviewed the development of the global semiconductor industry. The United States is the founder of semiconductors, and Moore's Law helped the early development of the U.S. semiconductor industry, making Intel the global semiconductor hegemon and maintaining it for a long time, because the world gathered resources to develop in accordance with Moore's Law.

However, "Success is Moore's Law, and failure is Moore's Law." Yang Guanglei said that Moore's Law promotes industrial division of labor and disintegrates the integrated component manufacturing (IDM) model. Semiconductor manufacturing is developing towards the East because manufacturing conflicts with the American innovation culture. This is the inevitable of the times. The phenomenon.

The United States was overtaken by Japan in the 1980s. Yang Guanglei said that Japan accounted for 50% of the global semiconductor market at its peak. However, the United States could not bear to be replaced, causing Japan to enter a lost 30 years. Not only did it lose its industry, it also caused a talent gap.

Yang Guanglei said that TSMC chose the unfavorable wafer foundry field. Because there was no competition, it was able to grow from a small company to a behemoth company. In the 1990s, Taiwan's stock dividend system attracted a wave of overseas returnees, and the Industrial Research Institute cultivated local talents in Taiwan, promoting the rapid development of the semiconductor industry. The epidemic has disrupted the global supply chain and made the world see the importance of Taiwan's semiconductors.

He pointed out that Taiwan's semiconductor industry is mainly based on manufacturing, and memory is mainly in Japan and South Korea. The upstream part is still dominated by Europe and the United States. Since most upstream companies have developed for nearly 40 years, China has been boycotted by the United States and needs to break through. The difficulty is extremely high, and it is estimated that it may face decades of difficulties.

Geopolitics has both negative obstacles and positive help for Taiwan's semiconductor industry. Yang Guanglei said that the risk mainly comes from the United States, because if the United States wants to reduce the risk of semiconductor manufacturing being concentrated in Asia, it will inevitably require TSMC to manufacture in the United States. Recently, it has been reported that the United States is urging TSMC to go to the United States. R&D, this is not a good thing for Taiwan.

Yang Guanglei said that globalization is dead and Taiwan must face it, maintain Taiwan's competitiveness, continue to develop, and break through unnecessary restrictions. Manufacturing in the United States will cause cost risks, and we should find ways to make up for the cost damage; forward-looking research is the strength of the United States, and we can cooperate with the United States in this regard. We should avoid conflicts with the United States and create lose-lose situations, and we must have intelligent dialogue.

Yang Guanglei said that non-U.S. regions such as Europe and Japan are full of opportunities; as for the huge problem in China, Taiwan may become farther and farther away from China, but China's huge market cannot be ignored. Taiwan should form alliances with countries around the world without compromising its competitiveness.

Yang Guanglei said that Taiwan is not a blue sky without dark clouds. Facing the crisis of declining birthrate, Taiwan should strengthen its productivity; in addition, it should seek a balance between energy and environment.

Regarding the subsidy policy, Yang Guanglei said that subsidies are the worst investment because the one-time subsidy is not enough and the return on investment is very poor. The best investment is investment in forward-looking research. He believes that Taiwan should not subsidize semiconductors as the icing on the cake.

Cao Shilun said that the whole world wants to develop semiconductors, but some countries are in competition with Taiwan. Therefore, Taiwan's semiconductor factories need a grand strategy for their international layout and cooperation, and they should consider taking active or passive strategies.

Xu Zunci emphasized that Taiwan has a complete semiconductor ecosystem and should remain in Taiwan. Facing geopolitical challenges, Taiwan needs a national-level strategy and cross-industry collaboration to find solutions.

台灣半導體可領先至 2032 年,專家:國際合作加強研發安全

半導體重要性提升為國家安全等級,歐、美等世界各國爭相補貼半導體產業發展。工研院產科國際所研究總監楊瑞臨認為,台灣半導體可望領先至 2032 年,在下世代半導體技術方面,台灣要與國際合作,並加強研發安全。 楊瑞臨表示,地緣政治因素持續不斷延燒,台灣半導體產業競爭力可以維持多久,備受各界關注。台積電將於...