Intel’s effort to split off its chipmaking unit as a successful standalone business is likely to take years, according to analysts who spoke to EE Times. The main problem will be making Intel Foundry Services (IFS) cost competitive with larger rival TSMC, they said.

“The yields are just really bad,” Bernstein Research senior analyst Stacy Rasgon told EE Times. He questioned whether Intel would see meaningful shipments of 18A chips by July 2027. Rasgon did not provide estimated numbers on Intel’s yields.

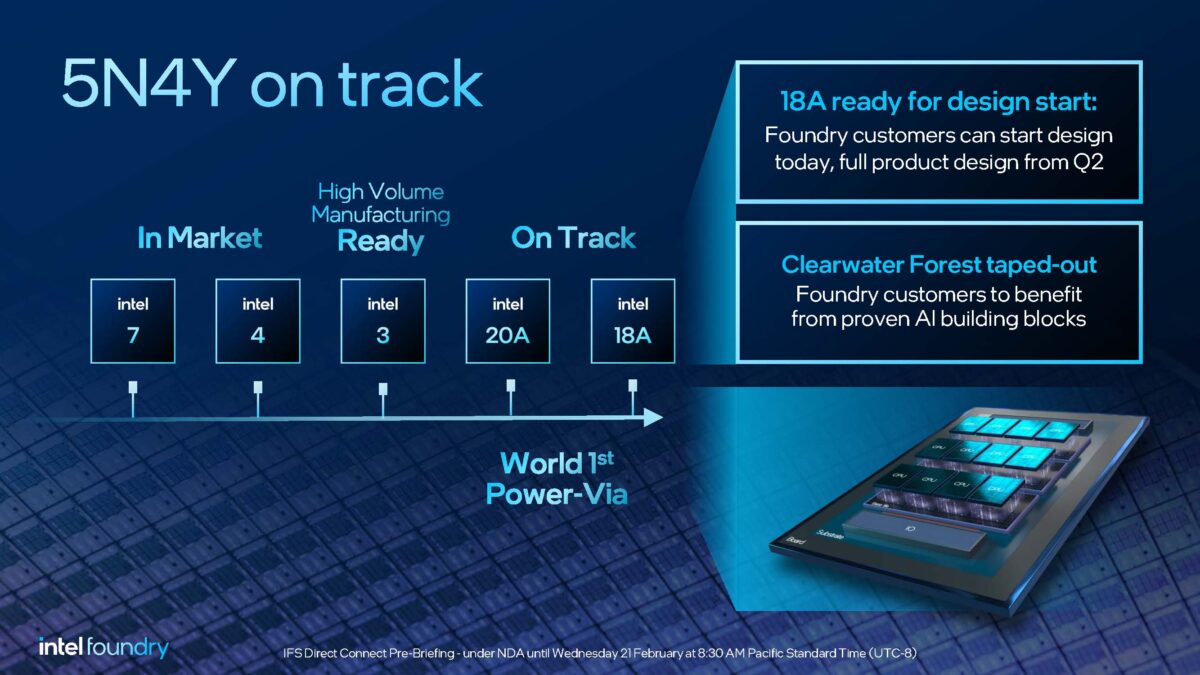

Intel’s first products made with 18A process technology, the destination on the company’s five-nodes-in-four-years roadmap, are coming in 2025, and the company last month released process design kit (PDK) 1.0 to prospective outside customers.

Yet the largest U.S. chipmaker last week said during a financial results announcement that it is cutting 15% of its headcount. Intel will slash 2024 capital expenditures for new fab capacity by more than 20% to a range of $25 billion and $27 billion, reflecting expectations for softer second-half demand.

The IFS operating loss of $2.8 billion in the second quarter this year was worse than the previous quarter. Intel said it expects operating losses at manufacturing unit IFS to continue at approximately the same rate in the third quarter, with more than 85% of wafer volume still coming from pre-EUV nodes with an uncompetitive cost structure. The company counts on its main rival and supplier, TSMC, to provide most of its advanced node chiplets made with EUV lithography.

The company said its ramp of Intel 4 and 3 processes at its Ireland fab, as well as elevated R&D and startup costs to support leading-edge technology development, will also weigh on profitability.

IFS sales to customers outside of parent company Intel remain insignificant, according to Rasgon.

“The initial ramp up is probably mostly packaging,” Rasgon said. “They gave some targets for external revenue. They’re aggressive. We’ve seen effectively nothing yet. They don’t have the processes yet. Especially if the bulk of the interest is going to be on 18A, they haven’t launched it yet.”

IFS cannot compete with larger rivals like TSMC and Samsung on a cost basis, Dylan Patel, chief analyst at SemiAnalysis, told EE Times.

“Eventually Intel can compete if they get more competitive in process technology, but that isn’t until 2026 at minimum in our view,” Patel said.

Intel will continue to rely on TSMC for advanced node silicon, Patel added.

“This is the most significant rebuilding of Intel since the transition from memory to microprocessors four decades ago,” Gelsinger said on an earnings call. “We firmly believe in the IDM 2.0 strategy.”

Intel CEO Pat Gelsinger (right) greets President Joe Biden at Intel’s future manufacturing site in Licking County, Ohio, on Friday, Sept. 9, 2022, as Intel celebrates the start of construction on the company’s newest U.S. manufacturing site. Intel is investing more than $20 billion in the new semiconductor manufacturing site to produce leading-edge chips. (Source:: Intel Corporation)

Intel revamped itself as an integrated device manufacturer (IDM) months after Gelsinger became CEO in 2021, calling for manufacturing expansions while opening more of its capacity for foundry services globally and increasing use of external foundries for some Intel products.

“The IDM 2.0 truck has now driven right into a wall, so to speak, and the company’s grandiose visions increasingly appear at odds with a much more muted reality,” Rasgon said in a report he provided to EE Times.

IFS faces challenges as an independent unit with its own profit-and-loss responsibility, analysts said.

“If Intel’s design side is rational, they will never go to IFS, and IFS will never have the volumes to cover the fixed costs,” Antipodes analyst Zobair Yaqubi told EE Times. “IFS needs to standardize as best it can to TSMC PDK design rules and get to near process parity and run at breakeven cost to get volumes in and build scale.”

Intel is building a new $20 billion facility in Ohio as part of its bid to support the CHIPS Act.

“We still believe that we’re comfortably able to execute against those milestones across the projects that we’ve announced,” Gelsinger said on the earnings call. “We are going to benchmark ourselves against world-class foundries, and that’s what Intel Foundry is going to become. That’s uncovered a lot of things, a lot of inefficiencies, a lot of ways that we can drive our capital footprint more effectively.”

Intel is analyzing every aspect of IFS, Gelsinger said. “How we do maintenance, how we procure chemicals, how we run and price wafers and shuttle lots. So, a clean-sheet analysis.”

Intel’s product businesses were not incentivized to make profitable choices in the past, Rasgon pointed out.

The Intel products side of the company has traditionally run “tons of expedites” trying to develop process technology, he added.

“I have to run test wafers, and I want them back very quickly from the factory. If you go to TSMC, they’ll do that for you, but you’ve got to pay for it. It costs a lot of money because it disrupts the fab. [Intel’s] product businesses were just sending tons and tons of expedites through the fabs because they didn’t care. They weren’t bearing the cost. The manufacturing side of the house is bearing the cost.”

Intel said that by 2026, it will cut costs by bringing back more of the business that it outsources to TSMC.

“The huge volume benefits of that really are in ‘26, where we’ll be very aggressive at bringing both the wafers home on a more competitive process with a more competitive product with Panther Lake offsetting the volumes of Lunar Lake, which is almost entirely outsourced,” Gelsinger said, referring to upcoming Intel processors. “We bring tiles (Intel parlance for chiplets) home with a more competitive product and a more competitive process.”

Analysts expressed doubts.

“We keep talking about bringing all these wafers back in-house to help gross margin in 2026, but I also hear about a lot more outsourcing to TSMC,” UBS analyst Timothy Arcuri said on the earnings call.

Intel has built capacity corridors for foundry customers, Gelsinger said.

“Until we have committed orders, we’re going to be modest on how much equipment we put in the [fab] shells and the sites that we have in place,” he replied to Arcuri. “How much of that corridor we keep available, how much flexibility working with our equipment suppliers that we need will be a subject of careful scrutiny as we go forward. The big thing is now that we’re finishing this phase of aggressive buildout.”

“The yields are just really bad,” Bernstein Research senior analyst Stacy Rasgon told EE Times. He questioned whether Intel would see meaningful shipments of 18A chips by July 2027. Rasgon did not provide estimated numbers on Intel’s yields.

Intel’s first products made with 18A process technology, the destination on the company’s five-nodes-in-four-years roadmap, are coming in 2025, and the company last month released process design kit (PDK) 1.0 to prospective outside customers.

Yet the largest U.S. chipmaker last week said during a financial results announcement that it is cutting 15% of its headcount. Intel will slash 2024 capital expenditures for new fab capacity by more than 20% to a range of $25 billion and $27 billion, reflecting expectations for softer second-half demand.

The IFS operating loss of $2.8 billion in the second quarter this year was worse than the previous quarter. Intel said it expects operating losses at manufacturing unit IFS to continue at approximately the same rate in the third quarter, with more than 85% of wafer volume still coming from pre-EUV nodes with an uncompetitive cost structure. The company counts on its main rival and supplier, TSMC, to provide most of its advanced node chiplets made with EUV lithography.

The company said its ramp of Intel 4 and 3 processes at its Ireland fab, as well as elevated R&D and startup costs to support leading-edge technology development, will also weigh on profitability.

IFS sales to customers outside of parent company Intel remain insignificant, according to Rasgon.

“The initial ramp up is probably mostly packaging,” Rasgon said. “They gave some targets for external revenue. They’re aggressive. We’ve seen effectively nothing yet. They don’t have the processes yet. Especially if the bulk of the interest is going to be on 18A, they haven’t launched it yet.”

IFS cannot compete with larger rivals like TSMC and Samsung on a cost basis, Dylan Patel, chief analyst at SemiAnalysis, told EE Times.

“Eventually Intel can compete if they get more competitive in process technology, but that isn’t until 2026 at minimum in our view,” Patel said.

Intel will continue to rely on TSMC for advanced node silicon, Patel added.

Steady as she goes

Despite the less than positive outlook, Intel CEO Pat Gelsinger is staying on course.“This is the most significant rebuilding of Intel since the transition from memory to microprocessors four decades ago,” Gelsinger said on an earnings call. “We firmly believe in the IDM 2.0 strategy.”

Intel CEO Pat Gelsinger (right) greets President Joe Biden at Intel’s future manufacturing site in Licking County, Ohio, on Friday, Sept. 9, 2022, as Intel celebrates the start of construction on the company’s newest U.S. manufacturing site. Intel is investing more than $20 billion in the new semiconductor manufacturing site to produce leading-edge chips. (Source:: Intel Corporation)

Intel revamped itself as an integrated device manufacturer (IDM) months after Gelsinger became CEO in 2021, calling for manufacturing expansions while opening more of its capacity for foundry services globally and increasing use of external foundries for some Intel products.

“The IDM 2.0 truck has now driven right into a wall, so to speak, and the company’s grandiose visions increasingly appear at odds with a much more muted reality,” Rasgon said in a report he provided to EE Times.

IFS faces challenges as an independent unit with its own profit-and-loss responsibility, analysts said.

“If Intel’s design side is rational, they will never go to IFS, and IFS will never have the volumes to cover the fixed costs,” Antipodes analyst Zobair Yaqubi told EE Times. “IFS needs to standardize as best it can to TSMC PDK design rules and get to near process parity and run at breakeven cost to get volumes in and build scale.”

CHIPS Act subsidy

Intel earlier this year won an $8.5 billion CHIPS Act subsidy that will be awarded by the Department of Commerce depending on the achievement of milestones aimed at helping rebuild the declining U.S. semiconductor industry.Intel is building a new $20 billion facility in Ohio as part of its bid to support the CHIPS Act.

“We still believe that we’re comfortably able to execute against those milestones across the projects that we’ve announced,” Gelsinger said on the earnings call. “We are going to benchmark ourselves against world-class foundries, and that’s what Intel Foundry is going to become. That’s uncovered a lot of things, a lot of inefficiencies, a lot of ways that we can drive our capital footprint more effectively.”

Intel is analyzing every aspect of IFS, Gelsinger said. “How we do maintenance, how we procure chemicals, how we run and price wafers and shuttle lots. So, a clean-sheet analysis.”

Intel’s product businesses were not incentivized to make profitable choices in the past, Rasgon pointed out.

The Intel products side of the company has traditionally run “tons of expedites” trying to develop process technology, he added.

“I have to run test wafers, and I want them back very quickly from the factory. If you go to TSMC, they’ll do that for you, but you’ve got to pay for it. It costs a lot of money because it disrupts the fab. [Intel’s] product businesses were just sending tons and tons of expedites through the fabs because they didn’t care. They weren’t bearing the cost. The manufacturing side of the house is bearing the cost.”

Intel said that by 2026, it will cut costs by bringing back more of the business that it outsources to TSMC.

“The huge volume benefits of that really are in ‘26, where we’ll be very aggressive at bringing both the wafers home on a more competitive process with a more competitive product with Panther Lake offsetting the volumes of Lunar Lake, which is almost entirely outsourced,” Gelsinger said, referring to upcoming Intel processors. “We bring tiles (Intel parlance for chiplets) home with a more competitive product and a more competitive process.”

Analysts expressed doubts.

“We keep talking about bringing all these wafers back in-house to help gross margin in 2026, but I also hear about a lot more outsourcing to TSMC,” UBS analyst Timothy Arcuri said on the earnings call.

Intel has built capacity corridors for foundry customers, Gelsinger said.

“Until we have committed orders, we’re going to be modest on how much equipment we put in the [fab] shells and the sites that we have in place,” he replied to Arcuri. “How much of that corridor we keep available, how much flexibility working with our equipment suppliers that we need will be a subject of careful scrutiny as we go forward. The big thing is now that we’re finishing this phase of aggressive buildout.”