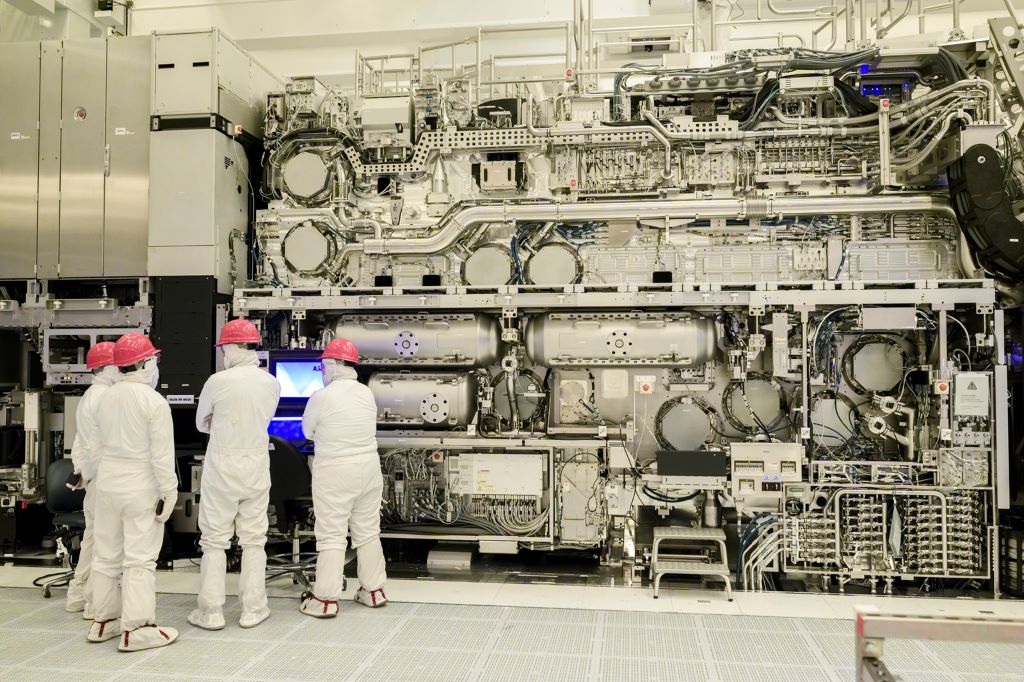

ASML's new CEO, Christophe Fouquet, attended the SPIE conference and delivered a speech focusing on the High NA EUV exposure machine. He also confirmed that Intel's second High NA EUV exposure machine has been assembled.

Christophe Fouquet stated that it is unlikely for the High NA EUV exposure machine to experience delivery delays like the current standard EUV exposure machines. The reason is that ASML has found a new method for assembling scanner sub-components: installing them directly at the customer's factory without the need for disassembly and reassembly. This approach will significantly save time and costs for both ASML and its customers, helping to accelerate the shipment and delivery of High NA EUV exposure machines.

Immediately following Christophe Fouquet was Intel Fellow and Director of Lithography Technology, Mark Phillips. He stated that Intel has completed the installation of two sets of High NA EUV exposure systems at its Portland factory. Moreover, Mark Phillips revealed some data showing that the improvements brought by the High NA EUV exposure machines compared to standard EUV exposure machines might be even greater than previously imagined.

Mark Phillips emphasized that, due to gained experience, the installation speed of the second High NA EUV exposure system was even faster than the first. It is reported that all the necessary infrastructure required for the High NA EUV exposure equipment is already in place and operational. Mask inspection work for High NA EUV exposure has begun as planned. Therefore, Intel can put it into production without much additional support work.

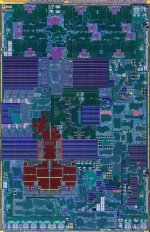

Additionally, Mark Phillips was asked about the issue of CAR (Chemically Amplified Resist) and metal oxide resists. He said that CAR is sufficient for now but may require metal oxide resists at some point in the future. Intel's goal is to have the Intel 14A process technology in mass production in 2026-2027, during which the process technology will be further enhanced.

technews.tw

technews.tw

Christophe Fouquet stated that it is unlikely for the High NA EUV exposure machine to experience delivery delays like the current standard EUV exposure machines. The reason is that ASML has found a new method for assembling scanner sub-components: installing them directly at the customer's factory without the need for disassembly and reassembly. This approach will significantly save time and costs for both ASML and its customers, helping to accelerate the shipment and delivery of High NA EUV exposure machines.

Immediately following Christophe Fouquet was Intel Fellow and Director of Lithography Technology, Mark Phillips. He stated that Intel has completed the installation of two sets of High NA EUV exposure systems at its Portland factory. Moreover, Mark Phillips revealed some data showing that the improvements brought by the High NA EUV exposure machines compared to standard EUV exposure machines might be even greater than previously imagined.

Mark Phillips emphasized that, due to gained experience, the installation speed of the second High NA EUV exposure system was even faster than the first. It is reported that all the necessary infrastructure required for the High NA EUV exposure equipment is already in place and operational. Mask inspection work for High NA EUV exposure has begun as planned. Therefore, Intel can put it into production without much additional support work.

Additionally, Mark Phillips was asked about the issue of CAR (Chemically Amplified Resist) and metal oxide resists. He said that CAR is sufficient for now but may require metal oxide resists at some point in the future. Intel's goal is to have the Intel 14A process technology in mass production in 2026-2027, during which the process technology will be further enhanced.

ASML:High NA EUV 組裝加速,英特爾裝完第二套

ASML 新任執行長 Christophe Fouquet 出席 SPIE 大會演講時,介紹 High NA EUV 曝光機,也確認英特爾第二套 High NA EUV 曝光機組裝完成。 Christophe Fouquet 表示,High NA EUV 將不太可能像標準 EUV 延遲交貨,因 AS...