On April 17, Mick Posner, Director of Product Marketing, IP Subsystems, Hardening & IP Kit solutions held a Webinar entitled ‘Getting more from your IP Vendor, IP Tuned to Your SoC’. This brought back memories of the challenges in days past of making the right choices in IP selection, integration and validation when prudence limited choices and necessity dictated over-design or schedule push-out to make sure nothing was overlooked. Even with that, there were some setbacks followed by workarounds or waivers or fixes or ‘bug-as-a-feature’ specifications.

Luckily, we are in a golden age of design where success is more the norm and discipline and methodology complement the availability of pre-designed, pre-verified IP that interoperates and simplifies the task of subsystem and system verification.

The webinar addressed silicon design trends, approaches to faster IP integration, IP software development acceleration, IP validation and bring-up, DesignWare IP from architecture to silicon.

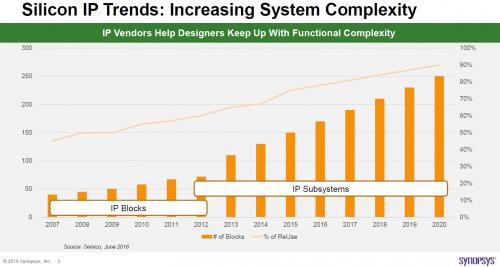

Increased System complexity has Silicon Design trends moving towards increased reuse of pre-designed and validated IP blocks and subsystems. This limits the task of verification to ensuring functionality at crossing boundaries of the IP interfaces and with this reduced exposure to implementation variability and increased consistency, the verification duration is reduced along with the functionality risk.

An IP Subsystem is far more complex than one realizes at first. As an example, one subsystem may contain more than a controller and PHY. You have unique logic intended to address clocking, reset, interrupts, DFT, security, and booting sequences to name a few. To address this, you need more than an RTL designer, you need expertise in layout, backend, test.

In addition, system level issues must be addressed like interface customization, interoperability, test and FPGA bring-up, interface simulation debug. Additional challenges exist like adequate throughput, latency, a timely schedule for tape out and silicon bring up.

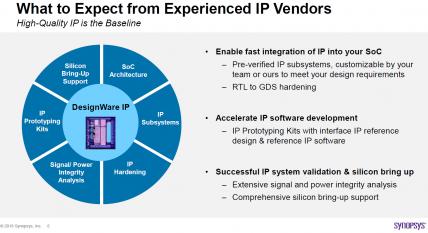

This is where your IP provider can increase the chances of success, allowing a fast integration of IP into your SoC, enabling the acceleration of IP software development and the experience to support comprehensive silicon bring-up.

From the initial critical decisions in architecting the SoC design where low power strategies, performance, and area can be gauged and optimized to leveraging protocol expertise of Synopsys IP R&D team, you are able to define the SoC correctly right from the start and implement it with the least amount of delay and the highest degree of confidence in proper implementation. Custom IP Subsystems tailor functionality to your requirements and accelerate your Time-to-Market with a reduced Design Risk.

A comprehensive provision of resources, test suites, monitors, synthesis scripts and integration documentation combine to make the integration of the IP subsystem as seamless as can be. Case studies from High-End Application Mobile Processor design with a high number of IPs and complex power domain shutoff to IP Hardening with Performance and size optimization, involving floor planning, clock balancing and timing analysis. Hardening services with Signal and Power Integrity on Low-Power, High-Performance Mixed-Signal are another example of the breadth and width of available assistance. Five days of SoC integration support come with the typical IP hardening effort.

IP Hardening Benefits

• Integration: Enables faster PHY and/or Subsystem integration

• Floorplan: Explore high-performance design to find an optimal solution for a given PHY

• Placement: Deal with a high power density in reduced core power areas

• CTS: Leverage access to custom cell development to meet performance targets

• Routing: Experience to allocate higher metal layers for critical signals for higher performance

DesignWare DDR PHY hardening projects in Wireless, Networking, Video, and Automotive applications have been supported in a wide range of process technology nodes.

Software IP Software Development acceleration is another important aspect of support of DesignWare prototyping kits enabling Reference Design and Reference Software Stack with the provision of immediate out-of-the-box hardware or software -only Kits. Expert support in Silicon Bring-Up is another aspect of the comprehensive Synopsys offerings.

The Synopsys Global IP Development and Support Organization includes 2400+ R&D engineers, 220+ Application engineers, and 30 Program Managers. These all accomplish the task of getting more from the IP Vendor, combining the customer vision and Synopsys expertise from Architecture to Silicon.

Register to view the webinar replay

Comments

There are no comments yet.

You must register or log in to view/post comments.