Synopsys issued a press release this morning that has some important news – Synopsys Introduces New 64-bit ARC Processor IP Delivering Up to 3x Performance Increase for High-End Embedded Applications. At first glance, one could assume this is just an announcement for some new additions to the popular ARC processor family. While that is true, there’s a lot more to the story. The newly announced processor IP has the potential to change the way embedded systems are designed.

I had the opportunity to chat with Mike Thompson, senior product marketing manager, ARC Processors at Synopsys. Before I get into more details, a bit about Mike. He drives the definition and marketing of the high-end ARC microprocessor products at Synopsys. Mike knows something about this market, having been involved in design and support of microprocessors, microcontrollers, IP cores, and the development of embedded applications and tools for over 30 years at places like MIPS, ZiLOG, Philips, AMD, and Actel. He holds a commanding view of the market and its needs.

One more important item before we dig into the details. Today, April 7, Mike is presenting the newly announcement processor IP at the Linley Spring Processor Conference, which is now a virtual event. His presentation is from 11:40 AM – 12:00 PM, Pacific time. I highly recommend you join that event if you’re registered for the conference.

“The growing complexity of high-end embedded systems such as in networking, storage, and wireless equipment demands greater processor functionality and performance without sacrificing power efficiency,” said Mike Demler, senior analyst at The Linley Group. “Synopsys’ new ARC HS5x and HS6x CPUs meet those needs, but they also provide the configurability and scalability needed to support future embedded-system requirements as well.”

OK, so why do I think is this announcement is a big deal? First, the basics. The following sentence from the press release says it well:

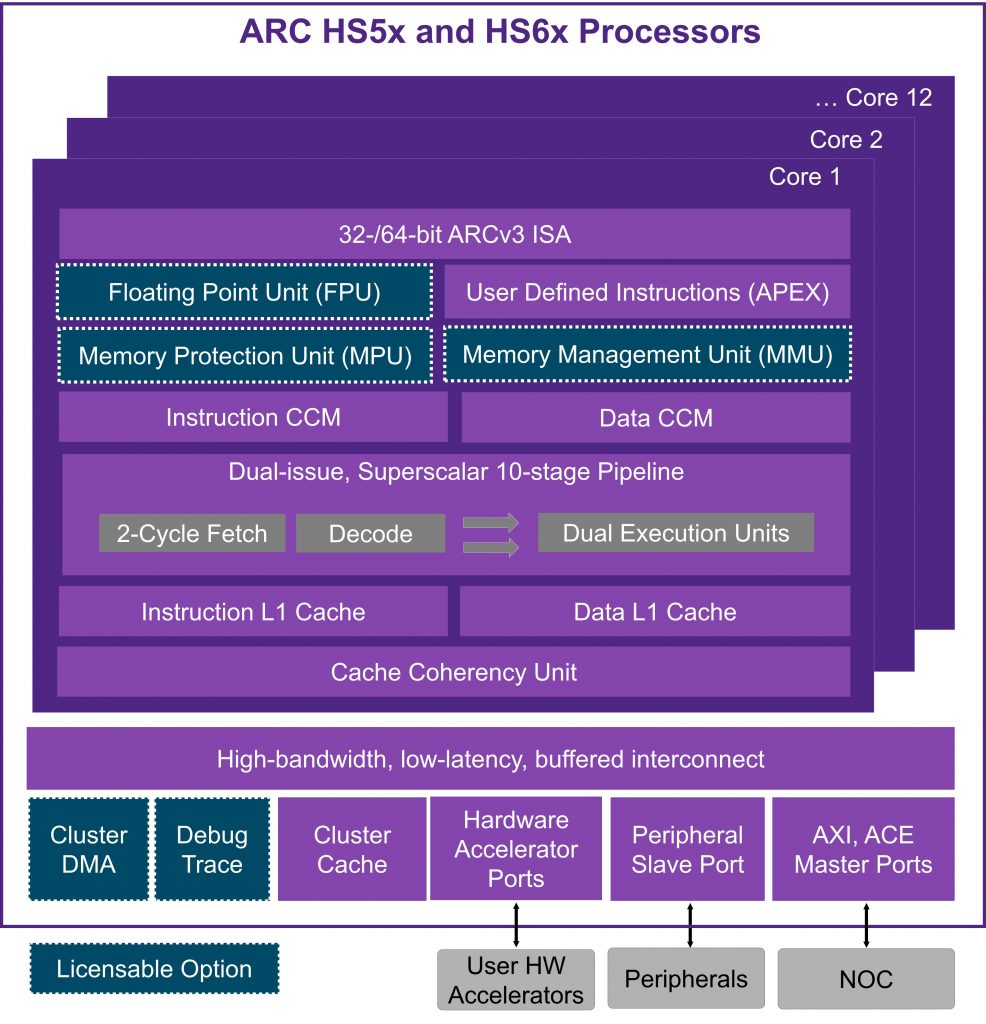

“The 32-bit ARC HS5x and 64-bit HS6x processors, available in single-core and multicore versions, are implementations of a new superscalar ARCv3 Instruction Set Architecture (ISA) and deliver up to 8750 DMIPS per core in 16-nm process technologies under typical conditions, making them the highest performance ARC processors to date.”

Setting a new performance bar is important, but that’s just the beginning of the story. These new processor cores extend capabilities in many directions, creating a new “canvas” if you will for embedded applications. Some capabilities make the job easier; some create fundamentally new opportunities. Regarding making the job easier, the 64-bit processor supports up to a 52-bit physical address space, which can directly address up to 4.5 petabytes. That’s a lot of room for innovation and significantly larger than anything else available.

There is support for up to 12 coherent CPU cores per processor cluster with L1 cache coherency. Mike explained that most applications today support four CPU cores, with a few offering up to eight. 12 cores, without degraded throughput, opens up the opportunity for new applications. The processors can be configured for real-time operation or with an advanced memory management unit (MMU) that supports symmetric multiprocessing (SMP) Linux and other high-end operating systems.

Another noteworthy capability is support for up to 16 user-implemented hardware accelerators with memory coherency. Hardware accelerators represent the “secret sauce” for many applications. Mike explained that few processors support hardware accelerators directly and those that do only support one. 16 changes the game. Mike listed some more features that make these processor cores extremely flexible and provide a lot of power optimization opportunities:

- Support for asynchronous clocking for all CPU cores and hardware accelerators that allows the cores to be clocked at different speeds than the interconnect and other cores in the processor cluster

- Support for individual power domains for all CPU cores, all hardware accelerators and the interconnect itself

- Support for the industry standard ACE interfaces to easily connect to a network-on-chip (NoC) that might be implemented in the SoC

- Coherency between the CPU cores with snooping, and coherency between the hardware accelerators with support for snooping

- Cluster shared memory, under software control that can be used to move data between the CPU cores, the hardware accelerators and the NoC

- High-bandwidth, low latency access to up to 16 MB of closely coupled memory (CCM) that is shareable between the CPU cores and hardware accelerators, providing single cycle access to local memory

At this point in our discussion, I felt that the application of these new cores was only limited by the imagination of the designer. This technology is quite complex – a direct quote from Mike drives the point home:

“We verify this IP with a few trillion vectors on a 100,000-server farm.”

I was starting to get dizzy. The new processors are backward compatible the EM, HS3x and HS4x processors, very convenient. Software development is supported by Synopsys’ ARC MetaWare Development Toolkit that includes an advanced C/C++ compiler optimized for the processors’ superscalar architecture, a multicore debugger to debug and profile code and a fast instruction set simulator (ISS) for pre-hardware software development. A cycle-accurate simulator is also available for design optimization and verification. Open-source software support for the processors includes the Zephyr real-time operating system, an optimized Linux kernel, the GNU Compiler Collection (GCC), GNU Debugger (GDB), and the associated GNU programming utilities (binutils).

ARC Processor EXtension (APEX) technology that enables the support of custom instructions is also included with these processors, as it is with all ARC processors. Mike mentioned that something like 80% of ARC users take advantage of this capability.

We also discussed the need many users have to understand what kind of performance they can expect from synthesizable IP in a particular technology. Mike described a very valuable service whereby Synopsys can run a benchmark implementation of a customer’s design in a target technology to reduce risk. I know from first-hand experience how important this can be.

The stated application areas for the new IP are: solid state drives (SSDs), wireless baseband, wireless control, home networking, cloud networking and edge networking. Given the strong support for hardware accelerators, I’ll be interested to see what new applications are invented by the customer base. As I mentioned, please connect to Mike’s presentation at the Linley Spring Processor Conference if you can.

Also Read:

Synopsys Tutorial on Dependable System Design

Use Existing High Speed Interfaces for Silicon Test

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.