SuperSpeed USB has been clearly ranked in the Interface protocols winner list, see this previous post. It could be interesting to dig into this IP market segment, determine in which applications USB 3.0 has been successfully deployed and who are the IP vendors serving this market, enabling SuperSpeed USB to take off.

SuperSpeed (SS) USB protocol is based on a physical layer offering a 5 Gbps speed, offering 4 GT/s effective bandwidth (due to 8b/10b encoding scheme), or 500 MB/s. This is about 10 times the High Speed (HS) bandwidth, and the protocol is very similar to PCI Express gen-2, in other words SS USB is a technology breakthrough when compared with HS USB. Thus, chip maker will carefully select the provider for USB 3.0 IP solution including the PHY and the Controller. The PHY selection should lower the overall risk, and the PHY IP should be as low power as possible… and available in the targeted technology, considering the many variants offered in the latest technology nodes: 40LP, 40G, 40LPG for TSMC 40 nm, or 28HP, 28HPM, 28HPL, 28LP for TSMC 28nm!

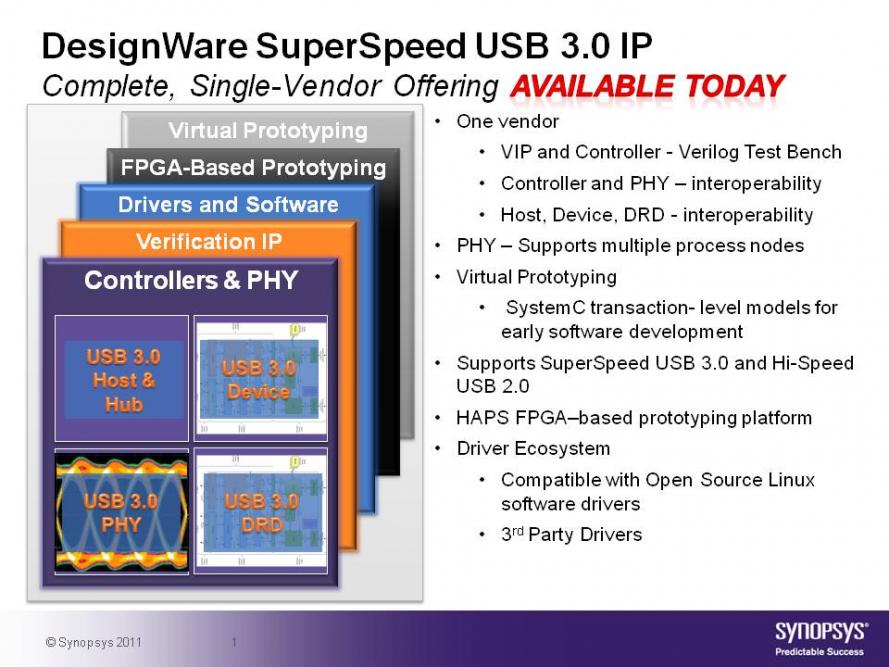

Moreover, when SuperSpeed USB was released, the backward compatibility constraint imposes to provide both USB 2.0 and USB 3.0 function to be 100% compatible, and the equation will be even more complex as you will have to select a vendor able to offer a proven USB 2.0 solution integrated with a (proven) USB 3.0 solution. Just as a reminder, the need to support both USB 2.0 and USB 3.0 has been fatal to some well-known and very capable IP vendors, like Snowbush for the PHY and PLDA for the Controller: both have exited the market in 2012, after having heavily invested since 2008, but with no success! Because Synopsys is the historical leader in USB IP market segment for almost ten years, the company is able to provide a single GDSII for the complete PHY, that is supporting the four speeds (LS to SS) in technology nodes from 130 nm to 28 nm, including 65 nm, 55 nm or 40 nm.

What is exactly the market addressed by USB 3.0, and using which solution between Host, Device or Dual? According with Synopsys, even if there is still a difference between the number of Controller and PHY IP sales, this is not surprising, we have shown that this market behavior is frequently seen in the Interface IP business, a majority of customers are buying today the “Integrated Solution”, PHY and Controller IP. Moreover, for USB 3.0, many customers go for the Dual solution, Host and Device capable.

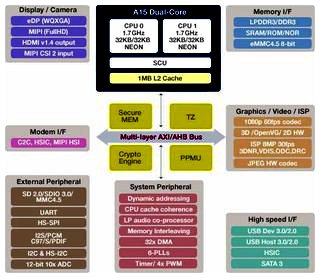

If the first design starts including SuperSpeed USB were for Hubs, Bridges and External storage, the market has now extended to WiFi dongle (to support WiFi 802.11ac specification, USB 2.0 is simply not offering enough bandwidth, and would generate a bottleneck!), and to Consumer Electronics products like HDTV and Blu-Ray high definition. The integration of SusperSpeed USB in Application Processors (AP) for smartphone and media tablet has started in 2011-2012, this can be verified by looking at the Samsung Exynos 5, supporting multiple USB3.0/2.0 ports (see the block diagram), so we expect many chip makers to launch new AP with SuperSpeed USB support for external interface capability, and we may also see AP supporting SSIC (joint specification issued by MIPI Alliance and USB-IF) allowing to support internal chip-to-chip communication based on USB 3.0 Controller associated with MIPI M-PHY.

According with Synopsys, the first Tape-out of a chip integrating SSIC has been completed in 2012, so we have to stay tuned, as more TO should follow in 2013. During 2012, Synopsys is claiming to have supported ten design starts integrating SuperSpeed USB in the Smartphone/Media tablet/Ultrabook segments.

This means that, four years after USB 3.0 specification being launched by USB-IF, SuperSpeed USB is finally coming to the mainstream, and we (IPNEST) expect to see a range of 60 to 75 Design Starts integrating USB 3.0 in 2013. This could be translated into USB 3.0 IP market (sub) segment weighting above $30 million, and a complete USB segment to be in the $75 million range. Clearly, an IP vendor like Synopsys is a major enabler for this SuperSpeed USB technology penetration of the mainstream market, with Design Starts in External Storage, USB Hubs, WiFi dongles, Blu-ray players, HDTV, smartphone, media tablet and certainly more to come…

Last minute: January 6, 2013, USB-IF has announced a new spec, enhancing SuperSpeed USB 3.0 up to 10 GT/s! “The USB 3.0 Promoter Group today announced development of a SuperSpeed USB (USB 3.0) enhancement that will add a much higher data rate, delivering up to twice the data through-put performance of existing SuperSpeed USB over enhanced, fully backward compatible USB connectors and cables. This supplement to the USB 3.0 specification is anticipated to be completed by the middle of this year. spec should deliver a 10 Gbps data rate.”

Eric Esteve from IPNEST

Share this post via:

Comments

0 Replies to “IP vendors enable SuperSpeed USB IP take off in 2012”

You must register or log in to view/post comments.