By Marko Suominen and Slava Zhuchenya of Siemens Digital Industries Software.

It’s often said that an orchestra without a conductor is just a collection of talented individuals making noise. The conductor’s role is to transform that potential cacophony into a unified, beautiful symphony. The same concept holds for complex integrated circuit (IC) verification.

The sheer scale and intricacy of modern chips present a formidable orchestration challenge to verification teams. It’s no longer just about running individual design rule checks (DRC) or layout versus schematic (LVS) runs; it’s about managing an entire symphony of verification tasks, often playing out across different teams, tools and timelines.

This escalating complexity has exposed a critical bottleneck: the lack of a cohesive, automated system to manage the entire verification workflow. Without a conductor for this intricate orchestra, teams often find themselves mired in manual coordination, resource contention and the constant risk of missed steps, all of which directly impact crucial time-to-market windows.

Chaos: The unorchestrated verification flow

Imagine a verification environment where each type of check—DRC, LVS, parasitic extraction, electrical rule checks (ERC), and more—is initiated and monitored in isolation. Design IPs arrive from various sources, each with subtle differences in conventions like text labels or bus bit separators. Engineers must manually track dependencies, prioritize jobs, and ensure that all necessary runs are completed in the correct sequence.

This fragmented approach leads to several pervasive challenges:

- Scale limitations: As designs grow, so does the volume of verification data. Manually managing thousands or even millions of violations, or processing results from dozens of individual runs, becomes overwhelming and error-prone.

- Context fragmentation: Without a unified view, engineers struggle to see the holistic picture of the verification process. Issues are addressed in silos, making it difficult to identify systematic problems or optimize the overall flow.

- Tedious manual management: The administrative burden on engineers is immense. Submitting jobs, checking statuses, managing licenses, and coordinating with other teams consumes valuable time that could be spent on actual design and debug.

- Inefficient resource utilization: Compute resources and expensive EDA tool licenses may sit idle or become bottlenecks due to uncoordinated job submissions, leading to suboptimal throughput and increased operational costs.

- Risk of missed steps: Human error is inevitable. In a manual environment, it’s easy for a critical check to be overlooked, a dependency to be mismanaged, or a run to be forgotten, leading to costly reruns or, worse, undetected design errors that surface late in the cycle.

These challenges highlight a fundamental truth: the efficiency of modern IC design is increasingly dependent on the efficiency of its verification workflow.

The rise of verification orchestration: A conductor for complexity

To overcome these hurdles, the industry is increasingly recognizing the need for dedicated verification workflow management or job orchestration solutions. These systems act as the central conductor, bringing order, automation, and predictability to the complex verification process.

A robust verification orchestration system typically offers:

- Unified control and monitoring: A single graphical user interface (GUI) provides a comprehensive view of all verification jobs, their status, and dependencies. This eliminates the need to jump between multiple tools or windows.

- Automated flow capture and execution: The ability to define and store entire verification flows as templates ensures that all necessary checks and tasks are included. Users can initiate complex sequences of jobs—sequential or parallel—with a single click, drastically reducing manual effort and the risk of human error.

- Intelligent resource management: Such systems can optimize the use of compute resources and licenses. Features like license queuing ensure that licenses are allocated efficiently, and the ability to stream out layout data once for multiple runs significantly reduces redundant I/O operations and overall runtime.

- Enhanced visibility and notifications: Centralized status monitoring and automated notifications (e.g., email alerts upon job completion) free engineers from constant manual checking, allowing them to focus on analysis and debug.

- Improved collaboration: By providing a consistent, shared view of the verification status and results, these systems foster better communication and collaboration across design and CAD teams.

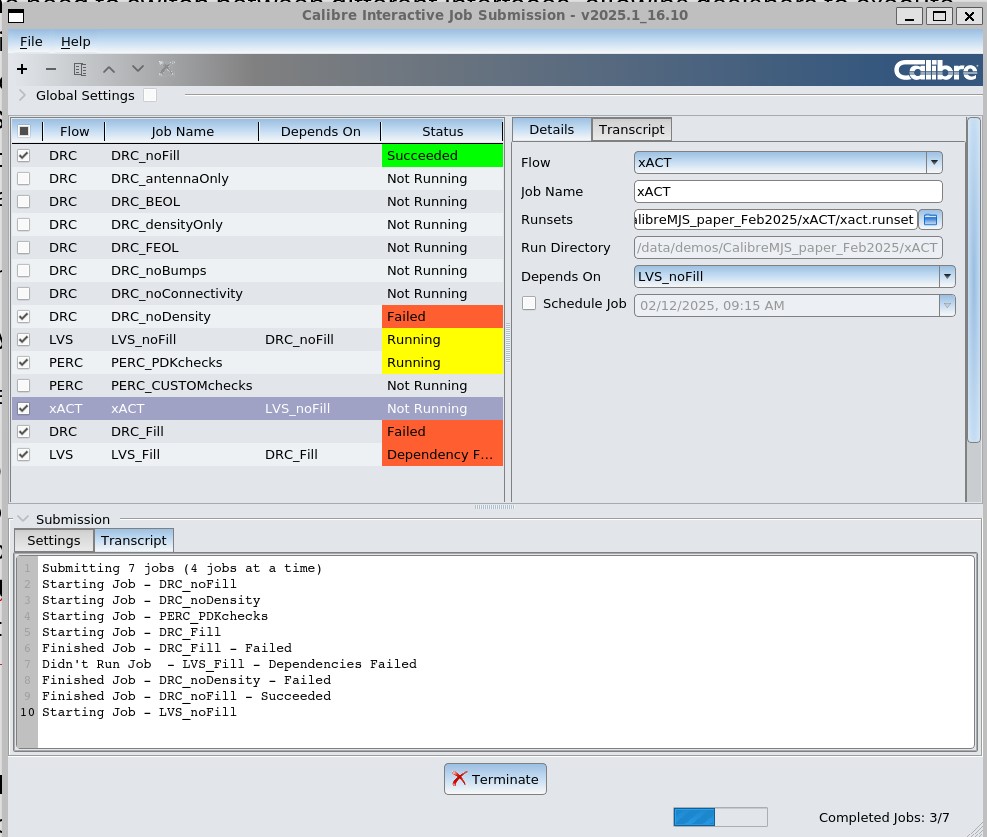

For instance, the Calibre Interactive Multiple Job Submission (MJS) GUI (Figure 1) is one such solution that exemplifies these capabilities. It allows design teams to intuitively manage and monitor all their verification jobs from a single interface, capturing entire sign-off flows into a single “Jobs Setup” file. This templated approach ensures that every aspect of the verification process is thoroughly accounted for, mitigating the risk of missed runs or checks.

Real-world impact: Streamlining verification for leading innovators

The practical benefits of adopting a verification orchestration approach are significant. A leading telecommunications company, for example, transformed its IC design verification workflows by adopting the Siemens Calibre MJS system. They experienced substantial improvements in automation, resource management and operational efficiency.

For top-level designers, the ability to automate and capture the entire verification flow meant eliminating manual initiation of multiple runs and reducing human error. Features like streamlined layout streaming (where the layout is streamed out only once for all runs) and efficient license usage (through license queuing and flexible allocation) directly contributed to faster throughput and optimized costs.

At the block level, the system provided a templated approach to physical verification (PV) flows, ensuring that no essential steps were overlooked. This “all-in-one” sign-off capability allowed designers to run all possible PV flows within a single platform, simplifying job submission and facilitating rapid iterations during design fixes.

The imperative of orchestration

As IC designs continue their trajectory of increasing complexity, the traditional, fragmented approach to verification is no longer sustainable. The ability to orchestrate the entire verification workflow, from individual checks to comprehensive sign-off, is becoming a non-negotiable requirement for competitive advantage.

By embracing a dedicated verification workflow management solution, design teams can move beyond manual overhead and reactive debugging. They can achieve greater efficiency, reduce the risk of costly errors, optimize valuable resources, and ultimately, accelerate their time-to-market. In the symphony of modern IC design, a capable conductor for verification is no longer a luxury, but an essential component for success.

Marko Suominen is a Calibre application engineer in Siemens Digital Industries Software and based in Helsinki, Finland. He helps his customers in the central and northern Europe to make successful IC design projects with Calibre products including more recent tools like Calibre 3D Thermal and Insight Analyzer. He received M.S in electrical engineering from Helsinki University of Technology (currently known as Aalto University). He could be reached at marko.suominen@siemens.com.

Slava Zhuchenya is a product engineer supporting Calibre interface tools in the Design-to-Silicon division of Siemens Digital Industries Software. His primary focus is the support and enhancement of the Calibre RVE and Calibre Interactive products. Previously, Slava was a member of the Calibre PERC R&D team. He received a B.S. in electrical engineering from Portland State University. Slava may be reached at slava_zhuchenya@siemens.com.

Also Read:

Breaking out of the ivory tower: 3D IC thermal analysis for all

Software-defined Systems at #62DAC

DAC TechTalk – A Siemens and NVIDIA Perspective on Unlocking the Power of AI in EDA

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.