Engineers love acronyms and my latest blog post has three acronyms in the title alone, so hopefully you are doing or considering SoC designs with the AMBA AXI4(Advanced eXtensible Interface 4) interface specification along with PCI Express (Peripheral Component Interconnect Express). One big motivation for using semiconductor IP and verification IP along with standards is that you can get your new product to market faster, with fewer bugs and using the minimum engineering effort. When you hear the phrase “Verification IP” your mind may quickly jump to vendors like Cadence or Synopsys, however Mentor Graphics is also in this business as well. Doing just a quick Google search on the phrase “Verification IP” turned up these three EDA vendors, along with SemiWiki in the #4 position:

Mentor produces something called the Verification Horizons Newsletter, where I read an article by David Aerne and Ankur Jain, “Fast Track to Productivity Using Questa Verification IP“. Here’s what to look for with any verification IP:

- Proven by multiple customers

- Checks for compliance to each protocol

- Has a compliance test suite

- Gives engineers analysis coverage

Related – Virtual Emulation Extends Debugging Over Physical

Integration

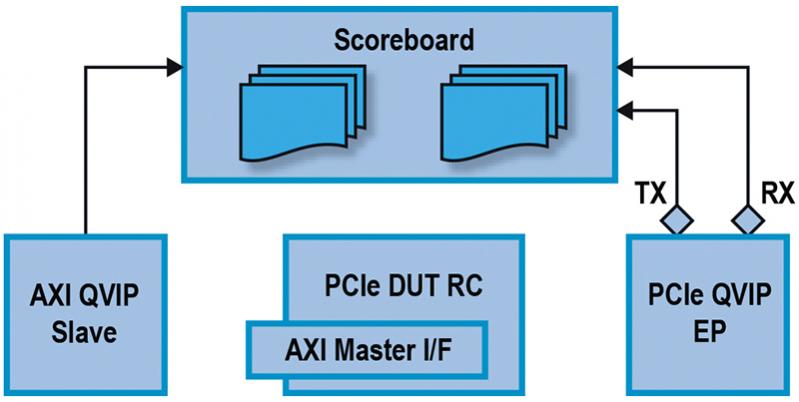

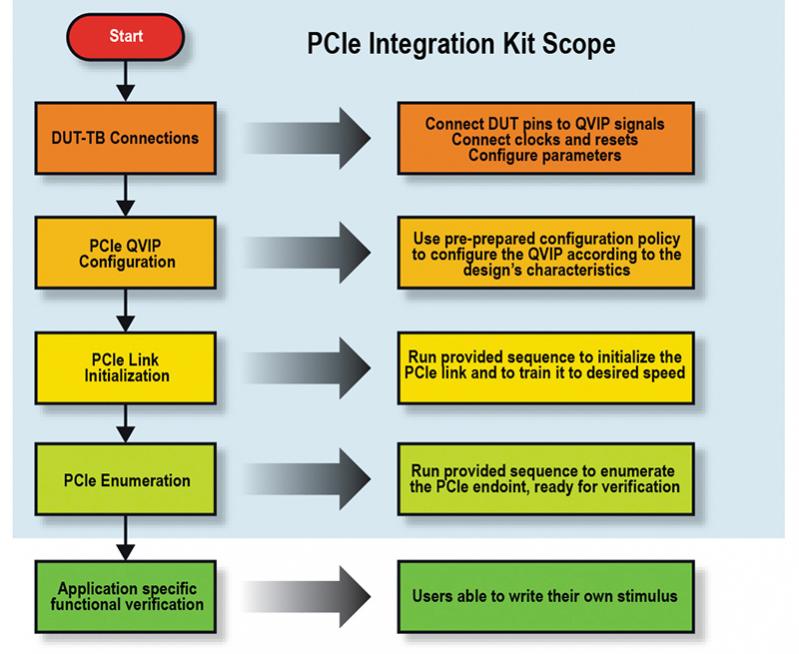

Let’s say that your DUT (Design Under Test) is a PCIe using RC (Root Complex). The design IP along with verification IP would look like this:

QVIP stands for Questa Verification IP, a Mentor product name. The QVIP has wrapper modules for each use case, making integration connection easier. Interface types supported for PCIe QVIP include: Serial, Pipe, PIE8 and MPCIe.

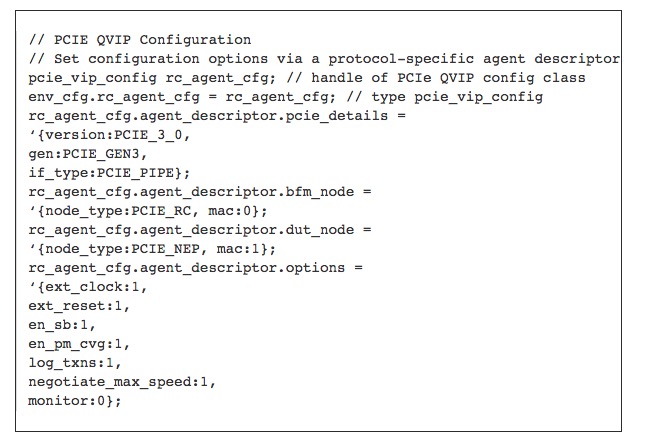

Configuration

Verification engineers can quickly configure each QVIP to model a PCIe End Point (EP) or Root Complex (RC) using a descriptor. This descriptor approach is quicker than writing UVM (Universal Verification Methodology) code to create analysis ports.

Related – UVM Debugging Made Easy & Productive in Questa

Here’s what an example PCIe QVIP configuration looks like:

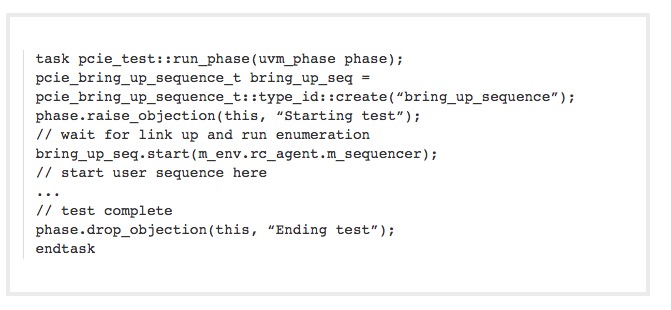

Further automation allows you to bring up a PCIe test bench using a sequence at a high level, shown in this code fragment:

Starter Kits

Buying your design IP and then getting them to work with Mentor’s QVIP is enabled through quick starter kits that allow you to install, instantiate, configure and bring up QVIP in a work day:

Related – A Functional Verification Framework Spanning Simulation to Emulation

APIs

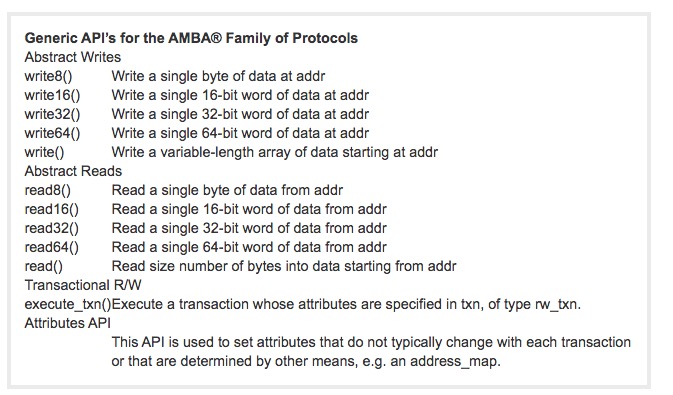

Generic APIs are provided that let you use read and write commands across all of the ARM AMBA protocols: AHB, AXI3, AXI4, ACE and CHI.

This generic API approach makes it easier to verify each SoC that uses ARM AMBA protocols.

Summary

Mentor Graphics does offer verification IP called QVIP that makes the task of SoC verification easier to bring up for the most popular protocols like AMBA AXI4 and PCIe bus interface. Connectivity modules, configuration, quick starter kits and portable utility sequences help automate the verification tasks. Monitors with QVIP ensure protocol compliance, and for analysis you get scoreboard and coverage collectors. Your verification team can track and achieve coverage goals by using the test suites and functional test plans.

Automation is your ally for verification, and Mentor’s QVIP can help. Read the full newsletter article here.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.