Custom IC design has demanding technical requirements to produce accurate simulation results for timing and power analysis in the shortest run times. EDA vendors have been rushing to use AI and ML technology to meet these analysis requirements. I attended a webinar from Siemens on accelerating iterative design cycles with Solido additive learning techniques to understand their approach to benefit custom IC designers.

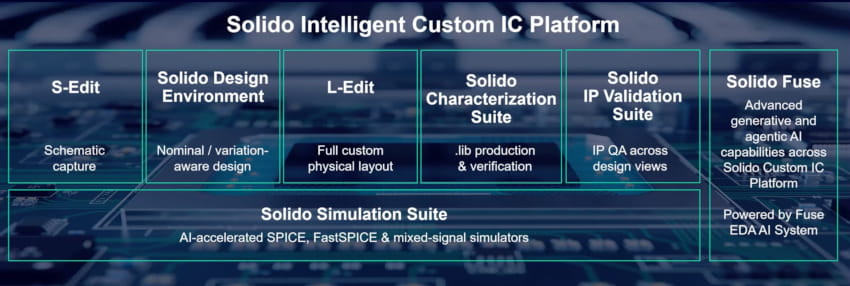

Mohamed Atousa, Product Management Manager at Siemens started with an overview of their custom IC platform with tools spanning from schematic capture, variation-aware design, physical layout, library characterization, IP QA, and SPICE simulation to generative and agentic AI.

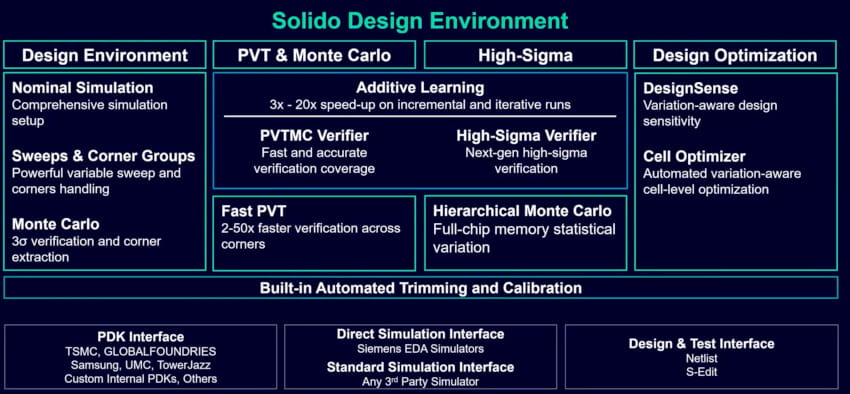

Within the Solido Design Environment are multiple analysis tools and the focus of this webinar was on the additive learning features used in PVTMC Verifier and the High-Sigma Verifier tools to achieve a 3X to 20X speed-up on incremental and iterative runs.

High-quality IC designs require variation-aware verification flows, yet the traditional Monte Carlo simulation methods run too slowly, but using extrapolation techniques cannot find outliers or model non-Gaussian behavior, and most simulation jobs are iterative. Making minor changes in a design or PDK require re-verification, creating verification flows that are too time consuming.

The new AI technologies enable SPICE-accurate variation-aware verification that is much faster than previous approaches. In the Solido PVTMC Verifier there is full coverage verification across PVT corners plus Monte Carlo, showing speedups of 2X to 10X, allowing it to find outliers that other methods can’t. AI used in Solido High-Sigma Verifier is able to produce 6-sigma yield verification in only thousands of circuit simulations, resulting in speed-ups from 1,000X to a Billion X faster than brute-force, all while maintaining SPICE accuracy.

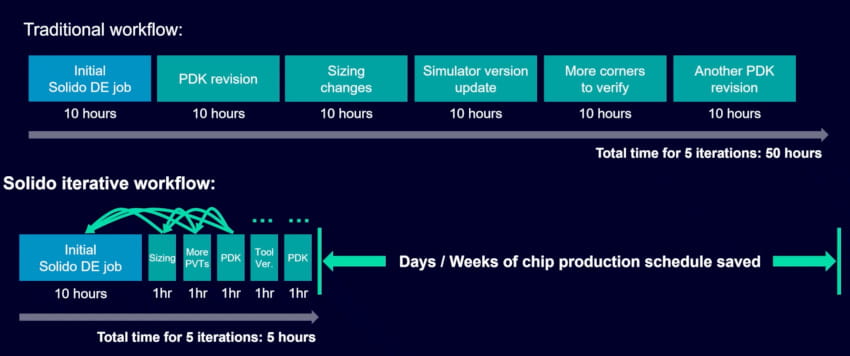

Jayne Alexander, Technical Product Manager at Siemens talked next about how additive learning technology retains and reuses AI models to speed-up iterative workflows by 3X – 20X. In a traditional workflow it is common to verify a design, then have to re-verify because of changes in: PDK revision, transistor sizing, simulator versions, adding more corners, etc. With the new iterative workflow there is still the first run, but subsequent verification run times are much reduced as previous results are stored for re-use.

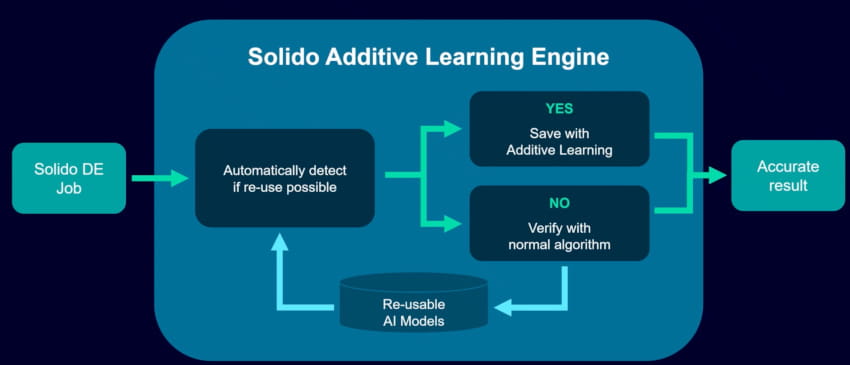

With the Solido Additive Learning Engine you experience accurate verification results every time, automatically. Here’s the internal flow chart to achieve this benefit.

This additive learning technology retains and reuses AI models from previous jobs to speed up iterative runs, making it fast and accurate while automating the process, while requiring no user-input or AI knowledge for the tool users. Under the hood there is an AI datastore that is designed to be light-weight and optimized, supporting multiple users at once, all while using small disk space.

From Microchip we heard from Amit Bansal, Technical Staff Engineer and their old iterative design process was taking 20-30 days. They ran PVTMC Verifier on bandgap reference circuits and RC oscillators, with and without Additive Learning (AL). For the bandgap reference circuit they made a design change on the pre-layout netlist then verified at 3 sigma across 21 PVT corners. The results were 3.7X fewer simulations, 4.1X wall clock speedup:

-

Base run – 885 simulations, 2hr 16min

-

AL off – 1,170 simulations, 3hr 24 min

-

AL on – 315 simulations (3.7X), 49min (4.1X)

In the RC oscillator example they changed the trim cap value in the post-layout netlist then verified at 3 sigma across 1 PVT corner. More impressive results with 20X fewer simulations, 18X wall clock speedup:

-

Base run – 300 simulations, 14 hr 16 min

-

AL off – 300 simulations, 11hr 40min

-

AL on – 15 simulations (20X), 39min (18X)

At DAC 2025 Microchip and Siemens presented their results in the Poster Gladiator Competition and won.

Summary

With verification times taking too long for custom IC designs with many iterations there has to be a better way than using brute-force Monte Carlo simulations and then waiting for answers. Thanks to AI-powered features like additive learning, the Solido tools have been shown to reduce the number of simulations by producing faster analysis answers, all while maintaining accuracy. Users can be productive quickly with no learning curve or AI expertise required, it’s out of the box easy with minimal to no user input required.

Watch the archived webinar online here.

Related Blogs

-

AI-Driven DRC Productivity Optimization: Insights from Siemens EDA’s 2025 TSMC OIP Presentation

-

DAC News – A New Era of Electronic Design Begins with Siemens EDA AI

Comments

There are no comments yet.

You must register or log in to view/post comments.