The Silicon Catalyst-Arm start-up contest winners were announced this week. This was the first contest of its kind so there was quite a bit of excitement. SemiWiki has worked closely with Silicon Catalyst for the past four years which has been quite the journey. Out of the one hundred plus companies SemiWiki has worked with over … Read More

Mastering Atomic Precision – ALD’s Role in Semiconductor Advancements

Atomic layer deposition (ALD) is a thin-film deposition method that continues to enable continuous advances in semiconductor device fabrication. Essentially, it involves exposing substrates sequentially to at least two different vapor phase atmospheres in which self-limiting reactions take place on the surface: the first… Read More

Blank Wafer Suppliers are not Totally Blank

AI requires more Silicon capacity

Deep in the supply chain, some wizards turn sand into perfect diamond-structured crystal disks of silicon, which are necessary for the entire semiconductor supply chain.

They are part of the semiconductor supply chain, making Silicon Sand almost a thousand times more valuable.

The glimmer … Read More

What’s all the Noise in the AI Basement?

My dog yawns every time I say Semiconductor or Semiconductor Supply Chain. Most clients say, “Yawn…. Don’t pontificate – pick the Nasdaq winners for us!”

Will Nvidia be overtaken by the new AI players?

If you follow along with me, you might gain some insights into what is happening in AI hardware. I will leave others to do the… Read More

The Case for U.S. CHIPS Act 2

Despite murky goals and moving targets, the recent CHIPS Act sets the stage for long term government incentives.

Authored by Jo Levy and Kaden Chaung

On April 25, 2024, the U.S. Department of Commerce announced the fourth, and most likely final, grant under the current U.S. CHIPS Act for leading-edge semiconductor manufacturing.… Read More

Top three challenges for global semiconductor manufacturing in 2024

Poised for recovery in 2024 and driving toward a historic $1 trillion in revenue, the global semiconductor industry has an incredibly promising future, backed by an unprecedented number of growth drivers, market opportunities, and technology advancements. Nevertheless, amid record greenfield capital investments and government-backed… Read More

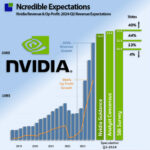

Ncredible Nvidia

This article previews Nvidia’s earnings release and will be updated during and after the earnings release. As usual, we will compare and contrast the Nvidia earnings with our supply chain glasses to identify changes and derive insights. Please return to this article, as it will be updated over the next week as we progress with our… Read More

Sarcina Teams with Keysight to Deliver Advanced Packages

All aspects of semiconductor design and manufacturing require collaboration across a global ecosystem. As complexity increases, so does the importance of good collaboration. This is especially true for advanced package design. Thanks to the movement to multi-die design, package development has become an incredibly difficult… Read More

2024 Starts Slow, But Primed for Growth

The global semiconductor market in 1Q 2024 was $137.7 billion, according to WSTS. 1Q 2024 was down 5.7% from 4Q 2023 and up 15.2% from a year ago. The first quarter of the year is typically down seasonally from the fourth quarter of the prior year. However, the 1Q 2024 decline of 5.7% was worse than expected.

Major semiconductor companies… Read More

A Webinar with Silicon Catalyst, ST Microelectronics and an Exciting MEMS Development Contest

Most MEMS and sensor companies struggle to find an industrialization partner that can support early-stage research and help develop and transition unique concepts to high-volume production. The wrong partner means delays and increased development costs as the design moves between various facilities. Recently, Silicon … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry