You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 178

[name] => IP

[slug] => ip

[term_group] => 0

[term_taxonomy_id] => 178

[taxonomy] => category

[description] => Semiconductor Intellectual Property

[parent] => 0

[count] => 1990

[filter] => raw

[cat_ID] => 178

[category_count] => 1990

[category_description] => Semiconductor Intellectual Property

[cat_name] => IP

[category_nicename] => ip

[category_parent] => 0

[is_post] =>

)

The tech world is sprinting toward a future where your fridge orders groceries, your car avoids traffic before you hit it, and security cameras don’t just watch—they understand. But behind these innovations lies a messy truth: building the brains for these smart systems is complicated.

Fresh off the 2024 Arm Tech Symposia… Read More

Dan is joined by Letizia Giuliano, Vice President of Product Marketing and Management at Alphawave Semi. She specializes in architecting cutting-edge solutions for high-speed connectivity and chiplet design architecture. Prior to her role at Alphawave Semi, Letizia held the position of Product Line Manager at Intel, where… Read More

Unlike traditional software programming, AI software modeling represents a transformative paradigm shift, reshaping methodologies, redefining execution processes, and driving significant advancements in AI processors requirements.

Software Programming versus AI Modeling: A Fundamental Paradigm Shift

Traditional… Read More

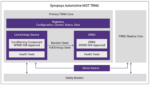

The security of a device or system depends mainly on being unable to infer or guess an alphanumeric code needed to gain access to it or its data, be that a password or an encryption key. In automotive applications, the security requirement goes one step further – an attacker may not gain access per se, but if they can compromise vehicle… Read More

The semiconductor ecosystem is changing. Monolithic design is becoming multi-die design. Processors no longer inform software development options. It’s now the other way around with complex AI software informing the design of purpose-built hardware. And all that special-purpose hardware needs drivers to make it come to … Read More

Tell us a little bit about yourself and your company.

I am Rui Tang, co-founder and VP of MSquare Technology. With a Ph.D. in Computer Engineering from Northeastern University and a master’s degree in management science and engineering from Stanford University, I bring over 23 years of experience in the IC industry. Prior to MSquare,… Read More

Last week, Synopsys announced an expansion of their Hardware-Assisted Verification (HAV) portfolio to accelerate semiconductor design innovations. These advancements are designed to meet the increasing demands of semiconductor complexity, enabling faster and more efficient verification across software and hardware… Read More

Artificial intelligence and machine learning have undergone incredible changes over the past decade or so. We’ve witnessed the rise of convolutional neural networks and recurrent neural networks. More recently, the rise of generative AI and transformers. At every step, accuracy has been improved as depicted in the graphic… Read More

The dominance of GPUs in AI workloads has long been driven by their ability to handle massive parallelism, but this advantage comes at the cost of high-power consumption and architectural rigidity. A new approach, leveraging a chiplet-based RISC-V vector processor, offers an alternative that balances performance, efficiency,… Read More

Paul Wells, CEO at sureCore, an ultra-low power memory specialist, has been involved in the semiconductor industry for over 35 years. Previously, he has worked as Director of Engineering for Pace Networks where he led a multidisciplinary product development team creating a broadcast quality video and data mini-headend. Before… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?