In the rapidly evolving landscape of semiconductor manufacturing, the demand for processors that handle increasing workloads while maintaining power efficiency and compact form factors has never been higher. Intel’s Foveros 2.5D packaging technology emerges as a pivotal innovation, enabling denser die integration… Read More

Smart Verification for Complex UCIe Multi-Die Architectures

By Ujjwal Negi – Siemens EDA

Multi-die architectures are redefining the limits of chip performance and scalability through the integration of multiple dies into a single package to deliver unprecedented computing power, flexibility, and efficiency. At the heart of this transformation is the Universal Chiplet Interconnect… Read More

Alchip’s 3DIC Test Chip: A Leap Forward for AI and HPC Innovation

Today Alchip Technologies, a Taipei-based leader in high-performance and AI computing ASICs, announced a significant milestone with the successful tape-out of its 3D IC test chip. This achievement not only validates Alchip’s advanced 3D IC ecosystem but also positions the company as a frontrunner in the rapidly evolving field… Read More

Intel Unveils Clearwater Forest: Power-Efficient Xeon for the Next Generation of Data Centers

At the recent Hot Chips conference, Intel® unveiled Clearwater Forest, its next-generation Xeon® 6 processor with efficiency cores (E-cores). The unveiling was made by Don Soltis, Xeon Processor Architect and Intel Fellow with over four decades of processor design experience and a long-standing contributor to the Xeon roadmap.… Read More

eBook on Mastering AI Chip Complexity: Pathways to First-Pass Silicon Success

The rapid evolution of artificial intelligence (AI) is transforming industries, from autonomous vehicles to data centers, demanding unprecedented computational power and efficiency. As highlighted in Synopsys’ guide, the global AI chip market is projected to reach $383 billion by 2032, growing at a 38% CAGR. This … Read More

Revolutionizing Chip Packaging: The Impact of Intel’s Embedded Multi-Die Interconnect Bridge (EMIB)

In an era dominated by artificial intelligence (AI), machine learning (ML), and high-performance computing (HPC), the demand for semiconductors that deliver high data throughput, low latency, and energy efficiency has never been greater. Traditional chip designs often struggle to keep pace with these requirements, leading… Read More

Breaking out of the ivory tower: 3D IC thermal analysis for all

Todd Burkholder and Andras Vass-Varnai, Siemens EDA

As semiconductor devices become smaller, more powerful and more densely integrated, thermal management has shifted from an afterthought to a central challenge in modern IC design. In contemporary 3D IC architectures—where multiple chiplets are stacked and closely arrayed—power… Read More

Chiplets: providing commercially valuable patent protection for modular products

Many products are assembled from components manufactured and distributed separately, and it is important to consider how such products are manufactured when seeking to provide commercially valuable patent protection. This article provides an example in the field of computer chip manufacture.

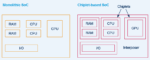

Chiplets

A system-on-a-chip

Streamlining Functional Verification for Multi-Die and Chiplet Designs

As multi-die and chiplet-based system designs become more prevalent in advanced electronics, much of the focus has been on physical design challenges. However, verification—particularly functional correctness and interoperability of inter-die connections—is just as critical. Interfaces such as UCIe or custom interconnects… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era