Keysight, with deep roots tracing back to Hewlett-Packard, has long been at the forefront of innovation in electronic design and testing. It manufactures electronics test and measurement equipment and software. The company also owns its own foundry and makes custom chips and packages for its instrumentation business. Many… Read More

What is Different About Synopsys’ Comprehensive, Scalable Solution for Fast Heterogeneous Integration

Multi-die design has become the center of a lot of conversation lately. The ability to integrate multiple heterogeneous devices into a single package has changed the semiconductor landscape, permanently. This technology has opened a path for continued Moore’s Law scaling at the system level. What comes next will truly be exciting.… Read More

Will 50% of New High Performance Computing (HPC) Chip Designs be Multi-Die in 2025?

Predictions in technology adoption often hinge on a delicate balance between technical feasibility and market dynamics. While business considerations play a pivotal role, the technical category reasons for the success or failure of a prediction are more tangible and often easier to identify—if scrutinized with care. However,… Read More

Heterogeneous 2D/3D Packaging Challenges

A growing trend in system design is the use of multiple ICs mounted in advanced packages, especially in high-performance computing and AI. These modern packages now integrate multiple ICs, often with high-bandwidth memory (HBM), resulting in hundreds of thousands of connections that need proper verification. Traditional… Read More

2025 Outlook with Larry Zu of Sarcina Technology

Tell us a little bit about yourself and your company.

I’m Larry Zu, Founder and CEO of Sarcina Technology. I’ve grown Sarcina from just designing packages for a few small companies to handling the entire post-silicon ecosystem, including package design, assembly, testing, qualification and production services for the top … Read More

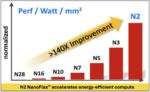

ML and Multiphysics Corral 3D and HBM

3D design with high-bandwidth memory stacks (HBM) has become essential for leading edge semiconductor systems in multiple applications. Hyperscalers depend on large AI accelerator cores supported by 100GB or more of in-package HBM to handle trillion parameter AI models. Autonomous Drive (AD) vehicles may handle smaller … Read More

TSMC Unveils the World’s Most Advanced Logic Technology at IEDM

There was a lot of discussion at IEDM about the coming shift to gate-all-around (GAA) transistor structures. This new device brings many benefits to continue device scaling, both at the monolithic device level as well as for multi-die design. The path to GAA is not simple, there are new material, process and design considerations… Read More

An Invited Talk at IEDM: Intel’s Mr. Transistor Presents The Incredible Shrinking Transistor – Shattering Perceived Barriers and Forging Ahead

IEDM turned 70 last week. This was cause for much celebration in the form of special events. One such event was a special invited paper on Tuesday afternoon from Intel’s Tahir Ghani, or Mr. Transistor as he is known. Tahir has been driving innovation at Intel for a very long time. He is an eyewitness to the incredible impact of the Moore’s… Read More

IEDM Opens with a Big Picture Keynote from TSMC’s Yuh-Jier Mii

The main program for the 70th IEDM opened on Monday morning in San Francisco with an excellent keynote from Dr. Yuh-Jier Mii, Executive Vice President and Co-Chief Operating Officer at TSMC. Dr. Mii joined TSMC in 1994. Since then, he has contributed to the development and manufacturing of advanced CMOS technologies in both fab

CEO Interview: Mikko Utriainen of Chipmetrics

Tell us about your company?

Chipmetrics is a Finnish company specializing in metrology solutions for high aspect ratio 3D chips, especially 3D NAND and 3D DRAM with an eye on GAAFET and CFET structures. We are a young but mature company founded in 2019 with over 40 customers worldwide, and we’re looking to further scale up our international… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry