You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Yesterday I talked to Shaker Sarwary, the senior product director for Atrenta’s clock-domain crossing (CDC) product SpyGlass-CDC. I asked him how it came about. The product was originally started nearly 8 years ago, around the time Atrenta itself got going. Shaker got involved about 5 years ago.

Originally this was a small… Read More

Aart de Geus was interviewed at the Goldman Sachs Technology Conference last week. Here is some of what he said. Strong Q1, good Q2 outlook, on-track for 2011 guidance. Strong rebound in Far East, Europe mixed, North America good. 80% revenue for year booked by start of year, 90% revenue for a quarter already booked at start of quarter.… Read More

Multiple, independent clocks are quintessential in SoCs and other complex ASICs today. In some cases, such as in large communications processors, clock domains may number in the hundreds. Clock domain crossings pose a growing challenge to chip designers, and constitute a major source of design errors–errors that can… Read More

EDA and Wall Streetby Paul McLellan on 02-11-2011 at 1:25 pmCategories: EDA

Good news in a way: Merrill Lynch (or Bank of America Merrill Lynch as I suppose we have to get used to calling them) have re-started coverage of EDA with a 20 page report on the industry, much of which is spent on explaining how the industry segments out and who is strong in which segments, stuff that most people reading this site already… Read More

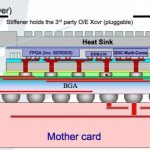

I attended the 3D architectures for semiconductor integration and packaging conference just before Christmas. I learned a lot and have put together an overview of what is going on in 3D ICs. This is not intended for experts (and if I’ve made egregious errors then please correct them in the forum) but more for people who are … Read More

EDA360 in PC Todayby Paul McLellan on 01-10-2011 at 8:29 pmCategories: Cadence, EDA

At the EDAC CEO panel, Daniel pointed out that he used EDA360 as a good introduction to non-specialists (e.g. financial sector). I just discovered today that the cover article of PC Today is by John Bruggeman (well, Cadence) about EDA360. Having some idea of just how difficult it is to get that sort of specialist article into a general… Read More

Solidohas run an interesting survey on variation-aware design. The data is generic and not specific to Solido’s products although you won’t be surprised to know that they have tools in this area.

What is variation-aware design? Semiconductor manufacturing is a statistical process and there are two ways to handle this in the design… Read More

One of the important but often unrecognized aspects of engineering is re-building the infrastructure underneath key design tools. Sometimes this gives a new desirable capability but often a lot of the effort is simply to modernize the code base so that it is possible to continue development effectively going forward. For example,… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?