You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Calibre is a well-known EDA tool from Siemens that is used for physical verification, but I didn’t really know how AI technology was being used, so I attended a Tuesday session at #62DAC to get up to speed. Priyank Jain, Calibre Product Management presented slides and finished up with a Q&A session.

In the semiconductor world… Read More

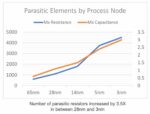

With advanced semiconductor processes continuing to shrink, the number and complexity of parasitic elements in designs grows exponentially contributing to one of the most significant bottlenecks in the design flow. Undetected parasitic-induced issues can be extremely costly, often resulting in tape-out delays.

Silvaco… Read More

On the last day of DAC 2025 I met with Chris Morrison, VP of Product Marketing at Agile Analog, to get an update. Their company provides Analog IP, the way you want it, and I knew that they had internal tools and a novel methodology to speed up the development process. This year they have started talking more about their internal IP automation… Read More

Power densities on chips increased from 50-100 W/cm2 in 2010 to 200 W/cm2 in 2020, creating a significant challenge in removing and spreading heat to ensure reliable chip operation. The DAC 2025 panel discussion on new cooling strategies for future computing featured experts from NVIDIA Research, Cadence, ESL/EPFL, the University… Read More

AI technology was prevalent at DAC 2025, but can we really trust what Generative AI (GenAI) is producing? Vishal Moondhra, VP of Solutions Engineering from Perforce talked about this topic in the Exhibitor Forum on Monday, so I got a front row seat to learn more.

Vishal started out by introducing the four challenges and risks of using… Read More

Modern SoCs can be complex with hundreds to thousands of IP blocks, so there’s an increasing need to have a front-end build and assembly methodology in place, eliminating manual steps and error-prone approaches. I’ve been writing about an EDA company that focuses on this area for design automation, Defacto Technologies, and … Read More

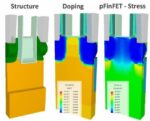

Semiconductor fabs aim to have high yields and provide processes that attract design firms and win new design starts, but how does a fab deliver their process nodes in a timely manner without having to run lots of expensive silicon through the line? This is where simulation and TCAD tools come into play, and to learn more about this… Read More

Modern vehicles have become quite sophisticated, like a supercomputer on wheels. They integrate a vast number of electronic components, including thousands of chips, to deliver advanced functionalities ranging from infotainment to critical safety systems. This increasing complexity necessitates a robust approach to … Read More

High-speed PCB designs are complex, often requiring a team with design engineers, PCB designers and SI/PI engineers working together to produce a reliable product, delivered on time and within budget. Cadence has been offering PCB tools for many years, and they recently wrote a 10-page white paper on this topic, so I’ll share … Read More

IC designs need to operate reliably under varying conditions and avoid inefficiencies like leakage across power domains. But how do you verify that connections between IP blocks has been done properly? This is where reliability verification, Electrical Rule Checking (ERC) tools and dynamic simulations all come into play particularly… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?