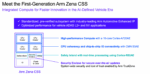

Last year Arm announced their support for standards-based virtual prototyping in automotive, along with a portfolio of new AE (automotive enhanced) cores. They also suggested that in 2025 they would be following Arm directions in other LOBs by offering integrated compute subsystems (CSS). Now they have delivered: their Zena… Read More

Author: Bernard Murphy

Arm Reveals Zena Automotive Compute Subsystem

Anirudh Fireside Chats with Jensen and Lip-Bu at CadenceLIVE 2025

Anirudh (Cadence President and CEO) had two fireside chats during CadenceLIVE 2025, the first with Jensen Huang (Founder and CEO of NVIDIA) to kick off the show, and later in the day with Lip-Bu Tan (CEO of Intel). Of course Jensen and Lip-Bu also turn up for other big vendor shows but I was reminded that there is something special about… Read More

Anirudh Keynote at CadenceLIVE 2025 Reveals Millennium M2000

Another content-rich kickoff covering a lot of bases under three main themes: the new Millennium AI supercomputer release, a moonshot towards full autonomy in chip design exploiting agentic AI, and a growing emphasis on digital twins. Cadence President and CEO Anirudh Devgan touched on what is new today, and also market directions… Read More

Optimizing an IR for Hardware Design. Innovation in Verification

Intermediate representations (IRs) between high level languages (C++, AI, etc.) and machine language are both commonplace (witness LLVM) and a continuing active area of research. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford,… Read More

Turnkey Multi-Protocol Wireless for Everyone

There is no IoT without wireless. If you have a great idea for a world-beating IoT device, you must integrate a wireless module (Bluetooth, Zigbee, Wi-Fi, UWB…) into that device. A ready-made companion wireless chip connected to MCU is one approach but will significantly increase unit cost and reduce profits. Products … Read More

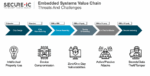

A Timely Update on Secure-IC

I last wrote about Secure IC back in 2023, a provider of embedded security technologies and services. Cadence announced at the beginning of 2025 their intention to acquire this company, which warrants a check-in again on what they have to offer. Secure-IC addresses multiple markets, from automotive, through defense/space and… Read More

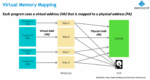

RISC-V Virtualization and the Complexity of MMUs

In the early days of RISC-V adoption, applications were microcontroller-centric with no need for virtualization support. But horizons expanded and now RISC-V is appearing in application processors, very much needing to be able to virtualize multiple apps concurrently. Take another step forward to datacenter servers running… Read More

LLMs Raise Game in Assertion Gen. Innovation in Verification

LLMs are already simplifying assertion generation but still depend on human-generated natural language prompts. Can LLMs go further, drawing semantic guidance from the RTL and domain-specific training? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO… Read More

Recent AI Advances Underline Need to Futureproof Automotive AI

The world of AI algorithms continues to advance at a furious pace, and no industry is more dependent on those advances than automotive. While media and analysts continue to debate whether AI will deliver value in business applications, there is no question that it adds value to cars, in safety, some level of autonomous driving, … Read More

Perspectives from Cadence on Data Center Challenges and Trends

From my vantage point in the EDA foxhole it can be easy to forget that Cadence also has interests in much broader technology domains. One of these is in data center modeling and optimization, through their Cadence Reality Digital Twin Platform. This is an area in which they already have significant track record collaborating with… Read More

Things From Intel 10K That Make You Go …. Hmmmm