The Semiconductor IP (Intellectual Property) lifecycle refers to the process by which design IP blocks—such as processors, memory controllers, interface PHYs, and verification models—are developed, verified, licensed, reused, and ultimately retired within the context of integrated circuit (IC) and SoC (System-on-Chip) development.

As modern chips become increasingly complex, the use of pre-verified IP blocks has become a cornerstone of semiconductor design productivity. The IP lifecycle ensures that IPs are developed, maintained, and delivered with quality, traceability, and compliance throughout their usable lifespan.

Overview

-

Semiconductor IP is a reusable unit of logic or cell design, often licensed from a third party or developed internally.

-

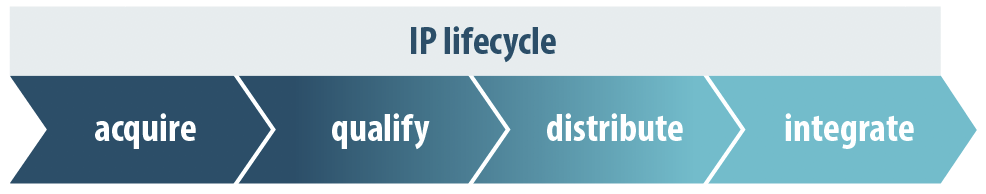

The IP lifecycle spans conception → development → validation → integration → production → EOL (End of Life).

-

IPs may be soft (RTL), firm (synthesizable netlists), or hard (physical layout for a specific node).

Lifecycle Stages

1. IP Specification

-

Define functionality, performance targets, interfaces, protocols, process nodes, PPA (power, performance, area), and safety/security goals.

-

Requirements driven by target markets (automotive, mobile, AI, etc.).

2. IP Design and Development

-

Coding in RTL (e.g., Verilog/SystemVerilog or VHDL)

-

Architecture design for reusability and configurability

-

Low-power design (UPF/CPF), clock-domain crossing (CDC), and functional safety (ISO 26262 for automotive)

-

Types:

-

Soft IP – synthesizable RTL (e.g., CPU cores)

-

Firm IP – netlists with timing info

-

Hard IP – GDSII for analog, PHYs, memories

-

3. Functional Verification

-

Simulation (unit, integration, regression)

-

Formal verification

-

Emulation / FPGA prototyping

-

Use of standardized verification IP (VIP) and UVM methodology

-

Metrics: coverage, bug rate, testability

4. IP Validation

-

Ensures compliance with relevant standards (e.g., PCIe, USB, DDR, Ethernet, AMBA)

-

Interoperability testing

-

Certification with industry consortia (JEDEC, MIPI, PCI-SIG)

-

Lint, CDC/RDC, and DFT (design for testability) checks

5. Packaging and Delivery

-

Creation of IP deliverables:

-

RTL files, synthesis scripts

-

Testbenches and coverage reports

-

Timing/power/area models (Liberty, LEF/DEF)

-

Documentation (integration guides, errata)

-

-

Delivered through secure IP management platforms (e.g., Cliosoft, Methodics)

6. IP Integration (at SoC level)

-

IP is instantiated into larger SoC designs using EDA tools (Synopsys, Cadence, Siemens)

-

Plug-and-play integration via standard buses (AMBA, TileLink, AXI)

-

IP configuration and parameterization for target use cases

-

Potential for hierarchical SoC builds using chiplets

7. Silicon Validation

-

IP verified in post-silicon environment:

-

Debug using JTAG, scan chains, or embedded monitors

-

Interoperability with real-world hardware (USB hosts, DRAM, etc.)

-

-

Performance, power, and reliability tested across voltage/temperature corners

8. Maintenance & Support

-

Bug fixes and updates for:

-

Silicon issues (errata)

-

Process migration (e.g., 7nm → 5nm)

-

Standards evolution (e.g., PCIe Gen4 → Gen5)

-

-

Support services include application engineering, customization, and on-site integration help

9. Reuse and Derivatives

-

IP may be:

-

Cloned into a derivative SoC

-

Used in multiple tape-outs across nodes or product lines

-

Enhanced (e.g., upgraded cache sizes, safety additions)

-

-

Tracking of versions and variants is handled through IP Lifecycle Management (IPLM) systems

10. Obsolescence (End of Life)

-

IP may be deprecated due to:

-

End of standards (e.g., USB 2.0)

-

Node obsolescence

-

Security vulnerabilities

-

-

Requires formal deprecation, removal from IP catalogs, and customer notification

Types of Semiconductor IP

| Category | Examples | Notes |

|---|---|---|

| Processor IP | RISC-V, Arm Cortex, DSP cores | Often configurable and soft |

| Interface IP | USB, PCIe, DDR, MIPI, Ethernet | Usually hard or mixed-type |

| Analog IP | PLLs, ADCs, SerDes, PMICs | Generally hard IP |

| Memory IP | SRAMs, ROMs, eFuses, MRAM | Custom-tailored to process |

| Security IP | Crypto accelerators, TRNG | Growing in IoT, automotive |

| Verification IP | PCIe VIP, AXI VIP | Used to test other RTL |

Key Players in the IP Industry

IP Providers

-

Arm – CPU, interconnect, GPU, subsystem IP

-

Synopsys – PHY, interface IP, security IP

-

Cadence – SerDes, memory, automotive IP

-

SiFive, Andes – RISC-V processor IP

-

Alphawave Semi, Rambus – High-speed PHY IP

-

Faraday, CEVA, Arteris, Imagination, Menta, CAST – Specialized IP

IP Management and Catalog Platforms

-

IP Lifecycle Management (IPLM) tools:

-

Methodics IPLM (Siemens EDA)

-

Cliosoft SOS

-

Arteris IP Explorer

-

Ecosystem Standards and Tools

| Area | Standards / Tools |

|---|---|

| IP Packaging | IP-XACT (IEEE 1685), DesignWare, CoreLink |

| Verification | UVM, SystemVerilog, VHDL |

| Compliance | PCI-SIG, JEDEC, MIPI, USB-IF |

| Security | ISO/SAE 21434, NIST FIPS, PSA-Cert |

| Safety | ISO 26262 (ASIL levels), FMEDA |

| Reuse Management | GIT/Perforce, IP lifecycle tools |

Challenges in IP Lifecycle Management

-

Version Control and Traceability: Maintaining history across nodes and projects

-

Integration Complexity: IP from different sources may not be fully compatible

-

Security: IP tampering, side-channel resistance, and secure provisioning

-

Legal Licensing: Managing usage rights, royalties, and export restrictions

-

Process Porting: Adapting IP from one technology node to another

-

Quality Assurance: Ensuring compliance with quality metrics (e.g., SPICE accuracy, IR drop, DRC clean)

Emerging Trends in IP Lifecycle

-

Chiplets: Modular, IP-based silicon integration via die-to-die protocols (e.g., UCIe)

-

AI-Driven Verification: ML tools assist in test generation and bug detection

-

Security-by-Design: IP-level encryption, authentication, and zero-trust strategies

-

Open-Source IP: e.g., RISC-V cores, OpenTitan—raising new lifecycle and trust concerns

-

Automated IP Cataloging: Integration with PLM/ERP and agile IC workflows

Things From Intel 10K That Make You Go …. Hmmmm