RISC-V is a free and open ISA enabling a new era of processor innovation through open standard collaboration. Born in academia and research, RISC-V ISA delivers a new level of free, extensible software and hardware freedom on architecture, paving the way for the next 50 years of computing design and innovation.

Importance of Open Source & Open Standards

Technology does not persist in isolation, unless we’re talking exceptionally simple unconnected devices like a flashlight – and even there, we rely on international standards to connect the battery to the bulb. As our technical world has become more complex and more connected, global standards ensure that society may realize the profound benefits of interoperability from the inventor to the consumer. Standards drive innovation at a base platform level from the standard threads on a machine screw to threads connecting silicon on a microprocessor. The setting of voluntary standards in engineering dates back more than a century. In the late 1980s through the 1990s, Tim Berners-Lee led a revolution to standardize the protocols we use on the internet (URL, HTML, HTTP, W3C), easily the biggest advance of technology utility in modern history. There are numerous examples that underpin the technology we rely on every day.

Advances in software and hardware standardization through global collaboration and consensus as well as open source development and delivery of software and hardware design has accelerated technical progress at an unprecedented global scale. The release of RISC-V to the open community for both standardization and ongoing improvement through open collaboration is at the core of the RISC-V Foundation. Without collaboration and open access to the RISC-V ISA and open extensions, the community risks fragmentation, forking, and the establishment of multiple standards. Such multiplicity diminishes the strategic value and longevity of the architecture as technology providers rely on global standards to advance partnerships and supply chains as well as participate in global markets for their products and services.

RISC-V Origin

Research at Berkeley

Prof. Krste Asanović and graduate students Yunsup Lee and Andrew Waterman started the RISC-V instruction set in May 2010 as part of the Parallel Computing Laboratory (Par Lab) at UC Berkeley, of which Prof. David Patterson was Director. The Chisel hardware construction language that was used to design many RISC-V processors was also developed in the Par Lab. The Par Lab was a five-year project to advance parallel computing funded by Intel and Microsoft for $10M over 5 years, from 2008 to 2013 1. It also received funding from several other companies and the State of California. While the project overall did not have Federal funding, Yunsup Lee and Andrew Waterman received some funding from the DARPA POEM photonics project , which funded some of the processor implementation development (but not the RISC-V ISA). The funds were 6.1 basic research via MIT as prime contract with the International Computer Science Institute as the subcontract. All the projects in the Par Lab were open source using the Berkeley Software Distribution (BSD) license, including RISC-V and Chisel. The following report of the Par Lab is the first publication that describes the RISC-V instruction set:

The RISC-V Instruction Set Manual, Volume I: Base User-Level ISA (EECS-2011-62)

Andrew Waterman, Yunsup Lee, David A. Patterson, and Krste Asanović, May 13, 2011.

For RISC-V, the UC Berkeley ParLab industrial sponsors provided the initial funding that was used to develop RISC-V. They didn’t explicitly ask for RISC-V itself, their interest was in parallel processing systems.

Beyond that first publication, major RISC-V milestones were the first tapeout of a RISC-V chip in 28nm FDSOI (donated by ST Microelectronics based in Switzerland) in 2011, publication of a paper on the benefits of open instruction sets in 2014 2, the first RISC-V Workshop held in January 2015, and the RISC-V Foundation launch later that year.

The ISA specification itself (i.e., the encoding of the instruction set) was effectively put into the public domain when the ISA tech reports were published, though the actual tech report text (an expression of the specification) was later put under a Creative Commons license to allow it to be improved by external contributors including the RISC-V Foundation.

No patents were filed related to RISC-V in any of these projects, as the RISC-V ISA itself does not represent any new technology. The RISC-V ISA is based on computer architecture ideas that date back at least 40 years. RISC processor implementations—including some based on other open ISA standards— are widely available from various vendors worldwide.

The worldwide interest in RISC-V is not because it is a great new chip technology, the interest is because it is a common free and open standard to which software can be ported, and which allows anyone to freely develop their own hardware to run the software. The Foundation does not manage or make available any open-source RISC-V implementations, only the standard specifications. RISC-V software is managed by the respective open source software projects.

Also see the original history article titled RISC-V Genealogy.

1 Patterson, D., Gannon, D. and Wrinn, M., 2013. The Berkeley Par Lab: Progress in the Parallel Computing Landscape. Microsoft Corporation.

2 Asanović, K. and Patterson, D. Instruction Sets Should Be Free: The Case For RISC-V (EECS-2014-146), August 6, 2014.

DARPA Influence

After the invention of RISC-V, many projects used it, including research programs funded by the Defense Advanced Research Projects Agency (DARPA), in many places and many companies. Open source standards provide great benefits to U.S. taxpayers in reducing the cost of advanced military system development, and also increases security by allowing the government to build their own trusted implementations at low cost. Note that several decades ago, the United States Air Force developed the open standard MIL-STD-1750 16-bit processor ISA for military applications for the same reasons (https://en.wikipedia.org/wiki/MIL-STD-1750A).

The UC Berkeley ASPIRE Lab succeeded the Par Lab, and was led by Krste Asanović. It lasted from 2013 to 2018 and led to the building of several RISC-V compatible microprocessors. It had funding from DARPA as well as from many companies. The DARPA funding was basic research funding (6.1 category).

Basic research funding to universities is largely for unrestricted research with permission to publically disseminate the results. This contract is the standard model for U.S. federal grants to universities, and allows for results from the funded work to be published in the open literature and made accessible to the public at large, worldwide. The government retains rights to use any technology developed in the research, but, unless explicitly stated, does not restrict the technology.

A related DARPA photonics program predates RISC-V and funded research at MIT in 2006. The research supported the development of integrated silicon photonics. Later stages of funding at MIT and Berkeley were used to build prototype chips, which included RISC-V cores as infrastructure to demonstrate the photonic links.

The ASPIRE Lab was funded by the DARPA Power Efficiency Revolution for Embedded Computing Technologies (PERFECT)program. The goal of the program was to develop revolutionary approaches as well as the technologies and techniques to provide the power efficiency required to enable embedded computing systems. Researchers used RISC-V based systems to demonstrate the ideas in that program.

In all of these funded projects, the RISC-V ISA specification and RISC-V open-source cores were not a contract deliverable. RISC-V was just the infrastructure separately developed to support the funded research.

While DARPA did not fund the original RISC-V ISA definition, DARPA funding played a significant role in its later development. The linked article on the SSITH Voting Machine and DOD presentation by Linton Salmon detail some of the areas where DARPA research continues to support RISC-V.

DARPA is currently funding a large set of programs around open-source hardware technology. The RISC-V Foundation has never had DARPA funding, nor pursued or received funding from any government.

RISC-V Foundation

The RISC-V Foundation (www.riscv.org) was founded in 2015 to build an open, collaborative community of software and hardware innovators based on the RISC-V ISA. The RISC-V Foundation, a non-profit corporation controlled by its members, directs the future development and drives the adoption of the RISC-V ISA. Members of the RISC-V Foundation have access to and participate in the development of the RISC-V ISA specification and extensions as well as related hardware and software. The Foundation has a Board of Directors composed of member representatives as well as a Technical Committee of work group leaders.

In November 2018, the RISC-V Foundation announced a joint collaboration with the Linux Foundation. As part of this collaboration, the Linux Foundation will provide operational, technical, and strategic support for the RISC-V Foundation which may include member management, accounting, training programs, infrastructure tools, community outreach, marketing, legal, and other open source services and expertise.

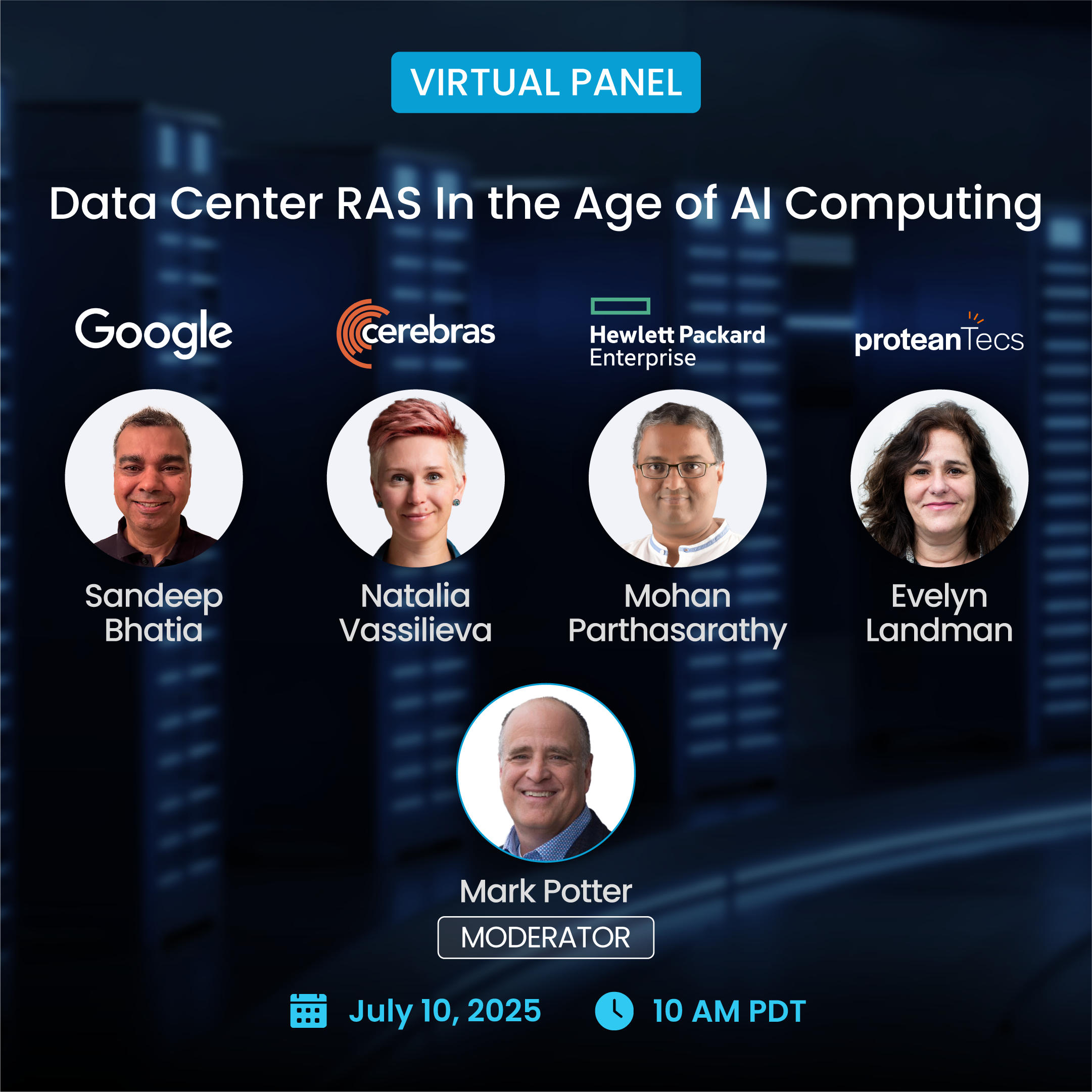

Each year, the RISC-V Foundation hosts global events to bring the expansive ecosystem together to discuss current and prospective RISC-V projects and implementations, as well as collectively drive the evolution of the surrounding hardware and software forward. Event sessions feature leading technology companies and research institutions discussing the RISC-V architecture, commercial and open-source implementations, software and silicon, vectors and security, applications and accelerators, simulation infrastructure and much more.

We encourage organizations, individuals, and enthusiasts to join our ecosystem and together enable a new era of processor innovation through open standard and open source collaboration.

Future Transition

After this four-year initial phase of the Foundation, the Board of Directors felt it was time to reorganize the Foundation to meet the increasing expectations of the rapidly growing RISC-V Community. This reorganization led to changes in membership levels, governance, meeting inclusiveness, and incorporation.

Membership level changes to expand engagement options and fund programming

Our new membership options will provide free, basic, and top level options to individuals and organizations. This change will allow more to participate in and grow the shared programming the Foundation may offer. The programming is an important variable to foster deep community commitment, solve shared challenges, and build industry opportunity.

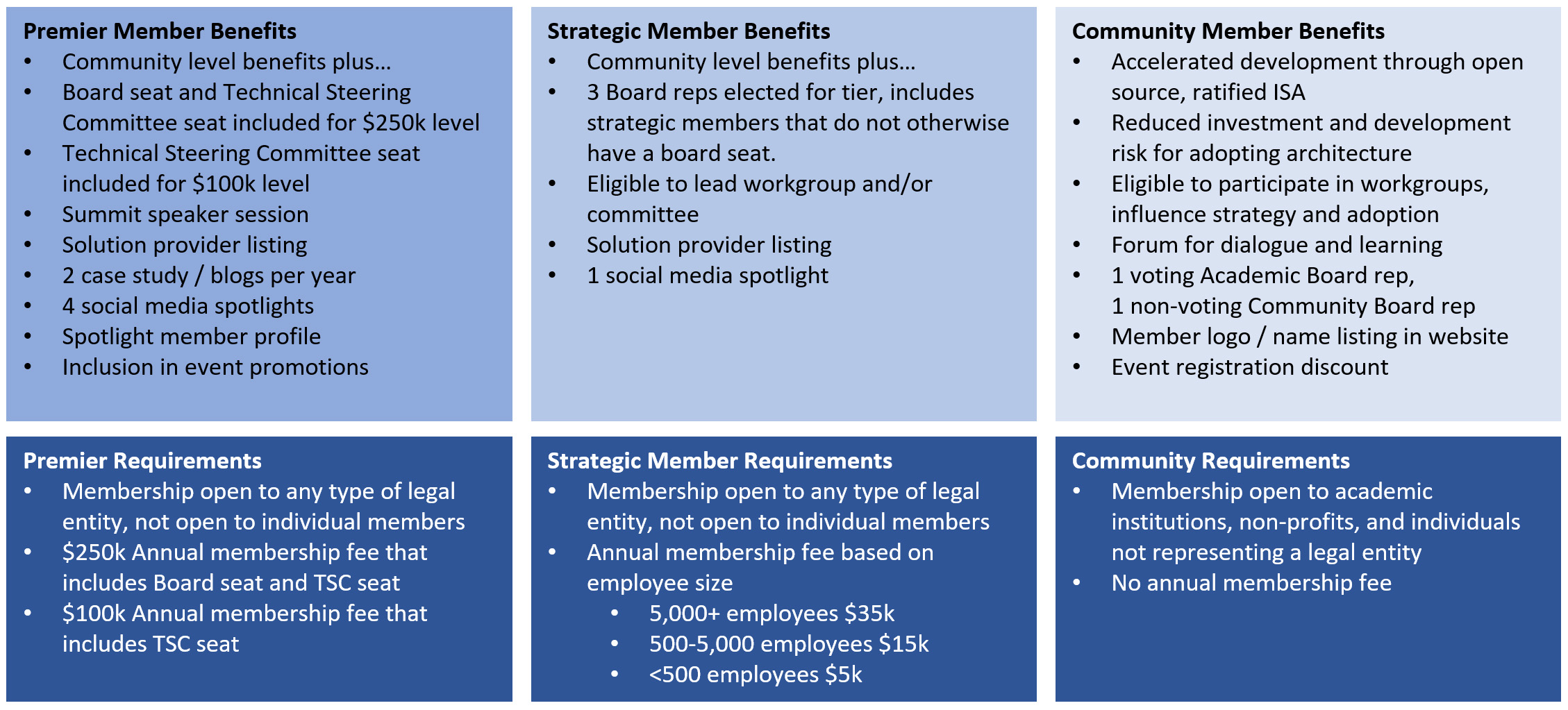

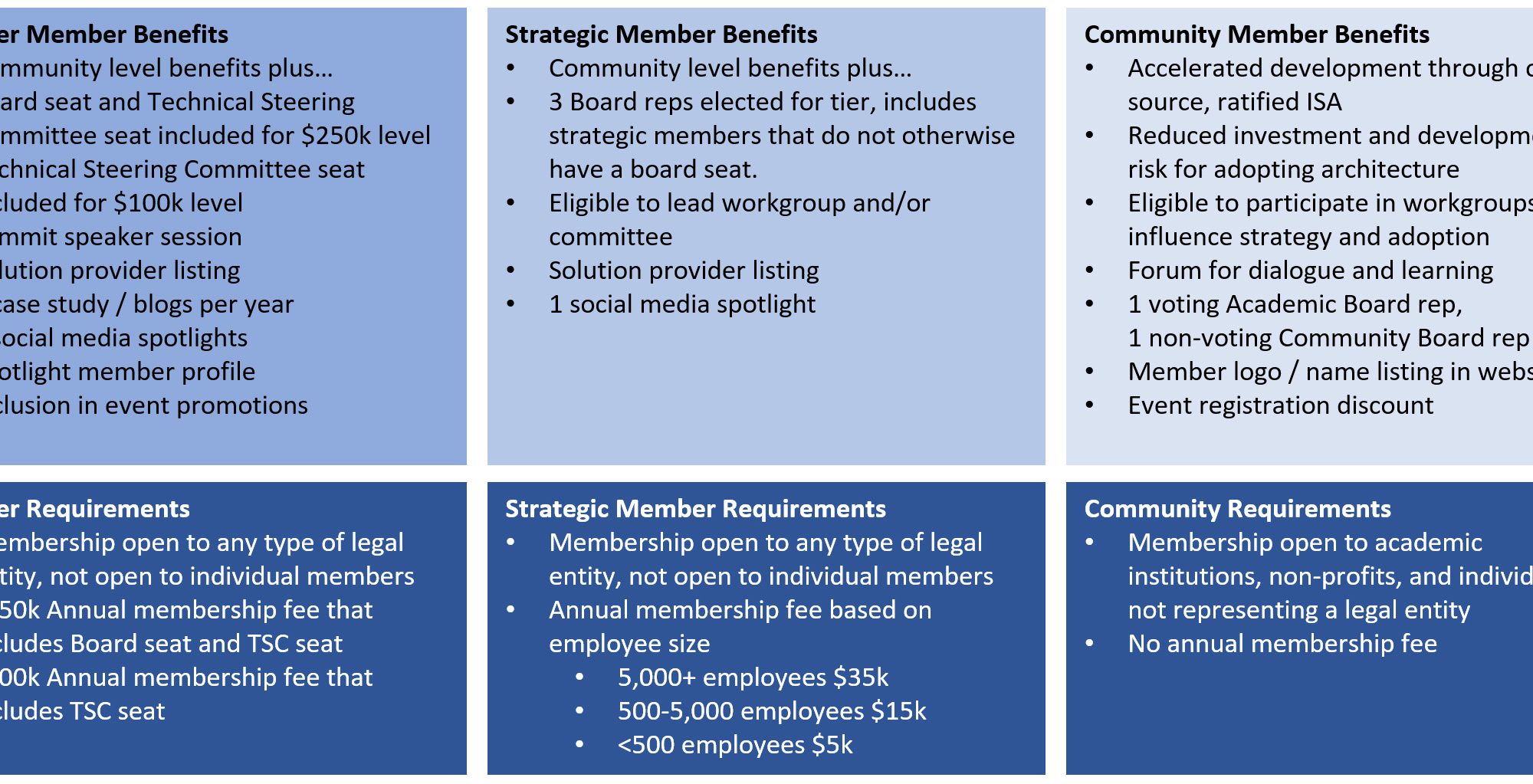

Membership levels

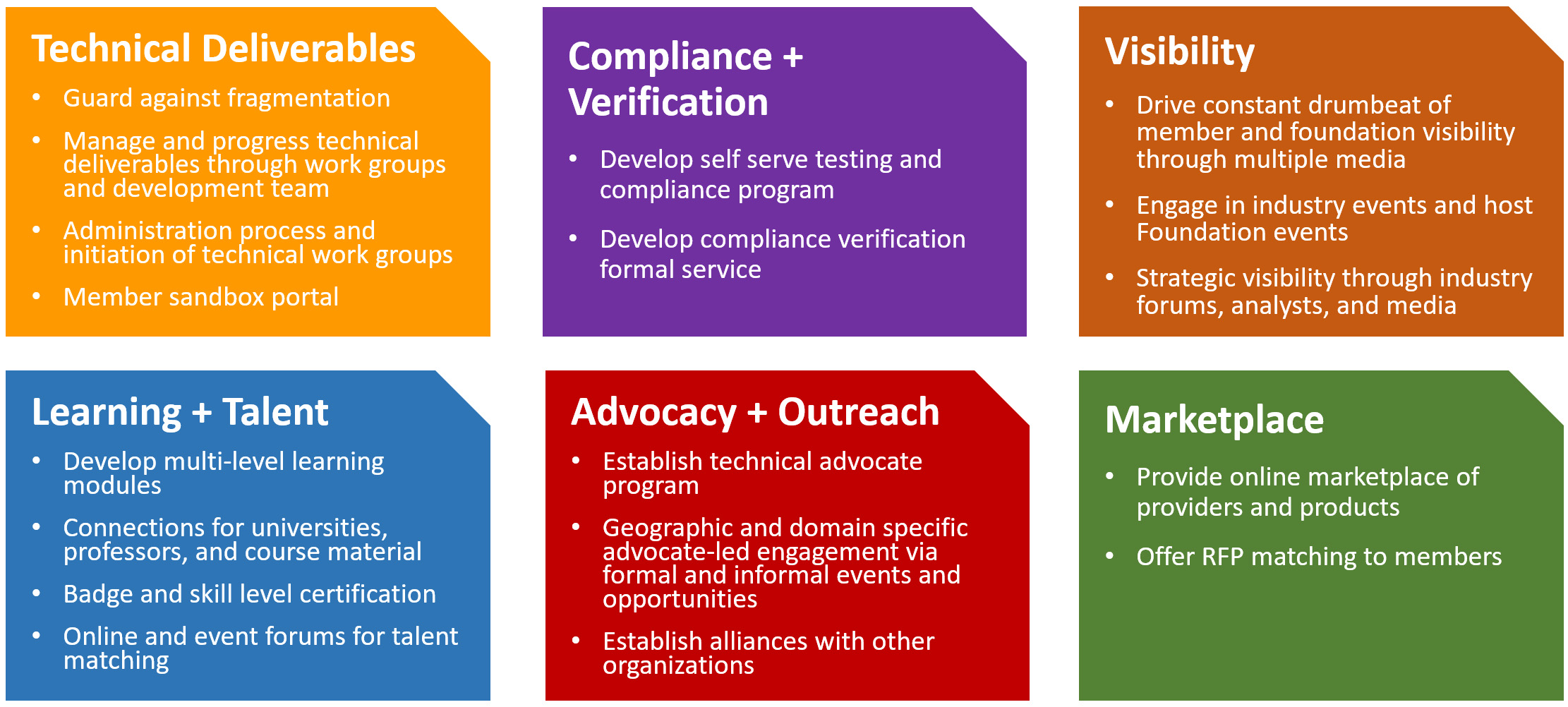

Proposed Programming

Governance shift to represent all levels of membership on Board of Directors and Technical Steering Committee

The governance structure will transition to an industry best practice of representation from every level of membership. This enables representative leadership across the membership in our Board of Directors and Technical Steering Committee through elected representation. The Board representation includes two directors from the Community level, three from the Strategic level, a director from Switzerland, and a director from each Premier member.

The Technical Steering Committee (TSC) will be composed of a technical chair from each of the technical work groups as well as a technical leader from each of the Premier members not otherwise represented. No member may have more than one representative on the Technical Steering committee. In cases where a member chairs more than one work group, the member organization may decide who their representative is.

The Foundation will hire a technical executive to facilitate priorities, navigate technical issues, and progress the technical strategy of the Foundation in collaboration with the TSC and work group leaders.

Switzerland incorporation alleviates geo-political uncertainty and reduces the likelihood of competing RISC‑V standards

Over the last year the RISC-V community has reflected on the geo-political landscape and we have heard concerns from around the world that investment in RISC-V must come with IP access continuity to ensure a long-term strategic investment. We first mentioned our intentions to move at the December 2018 summit. Incorporation in Switzerland has the effect of calming concerns of political disruption to the open collaboration model. The RISC-V foundation does not maintain any commercial interest in products or services as a non-profit, membership organization. There have not been any export restrictions on the Foundation in the US and we have complied with all US laws. The move does not circumvent any existing restrictions, but rather alleviates uncertainty going forward.

The Foundation is not incorporating in Switzerland based on any one country, company, government, or event. This move is reflective of community concern and managing strategic risk for our community investing in RISC-V for the next 50+ years. The jurisdiction of the Foundation has bearing only on the Foundation’s ability to facilitate global collaboration. The move reduces concern that a government would restrict the actions of an open source organization.

The IP contributed and produced by the Foundation is held under industry and global standard licenses that are already open to leverage by any company regardless of jurisdiction. This licensing is a common open source approach to foster collaboration that is not tied to any geographic regulation. Open Source IP has not been subject to export control.

Restricting access or reducing collaboration opportunities has the negative effect of encouraging organizations to develop unique foundational technology, also known as “forking”, or development of multiple standards or technical assets. By ensuring long-term, broad, and open participation, we are fostering a deep and sustainable shared RISC-V roadmap with a set of common elements for organizations to take a modular approach for implementation. A modular approach to technology requires open, transparent, and standard interfaces and instructions between parts for interoperability and strategic longevity.

Share this post via:

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot