Overview

| Feature | Intel 3 | Intel 18A |

|---|---|---|

| Node Class | Enhanced 7nm (refinement of Intel 4) | 1.8nm-class full-node leap |

| Transistor Type | FinFET | RibbonFET (GAAFET) |

| Power Delivery | Front-side power only | Backside Power Delivery (PowerVia) |

| EUV Use | Partial (select layers) | Extensive EUV, reduced multi-patterning |

| PPA Target | Modest vs. Intel 4 | +10–15% perf, –25–30% power vs. Intel 3 |

| HVM Timeline | 2023–2024 | 2025+ (internal first, external foundry late) |

Technology and Transistor Architecture

Intel 3

-

Derivative of Intel 4 (7nm-class), offering:

-

Slight scaling improvements

-

Performance-per-watt gains

-

Refined FinFET transistors

-

-

Targets Intel internal products and select foundry customers

-

Still uses traditional front-side power delivery

Intel 18A

-

A true next-generation node

-

Introduces:

-

RibbonFET (Intel’s implementation of Gate-All-Around FETs)

-

PowerVia (first backside power delivery on a leading-edge process)

-

-

Provides major advantages in:

-

Electrostatics

-

Area efficiency

-

Signal integrity and routing density

-

Performance, Power & Density (PPA)

| Metric | Intel 3 | Intel 18A |

|---|---|---|

| Performance | ~+18% over Intel 4 | +10–15% over Intel 3 |

| Power | ~–18% power vs Intel 4 | ~–25–30% vs Intel 3 (at same performance) |

| Density | Incremental over Intel 4 | Full-node gain: much smaller standard cell area |

| SRAM Scaling | ~10–15% | Optimized bitcells for GAA era |

PowerVia vs. Front-side Power

| Feature | Intel 3 | Intel 18A |

|---|---|---|

| Power Delivery | Front-side (traditional) | Backside (PowerVia) |

| Routing Area | Signal + power metal layers | Signal-only (cleaner routing) |

| Benefits | Mature & lower risk | Better power integrity, reduced congestion |

| Design Tools | Standard EDA flow | Requires PowerVia-aware flow (enabled via Intel Foundry) |

Design Ecosystem

| Element | Intel 3 | Intel 18A |

|---|---|---|

| EDA Enablement | Synopsys, Cadence, Siemens, Ansys (DFX tools) | Same partners + enhanced tools for PowerVia/GAA |

| IP Ecosystem | Arm (limited cores), Intel IP | Arm Cortex, PCIe Gen5/6, DDR5/LPDDR5X, AI IP |

| Packaging Options | EMIB, FCBGA | EMIB, Foveros Direct, UCIe (chiplets) |

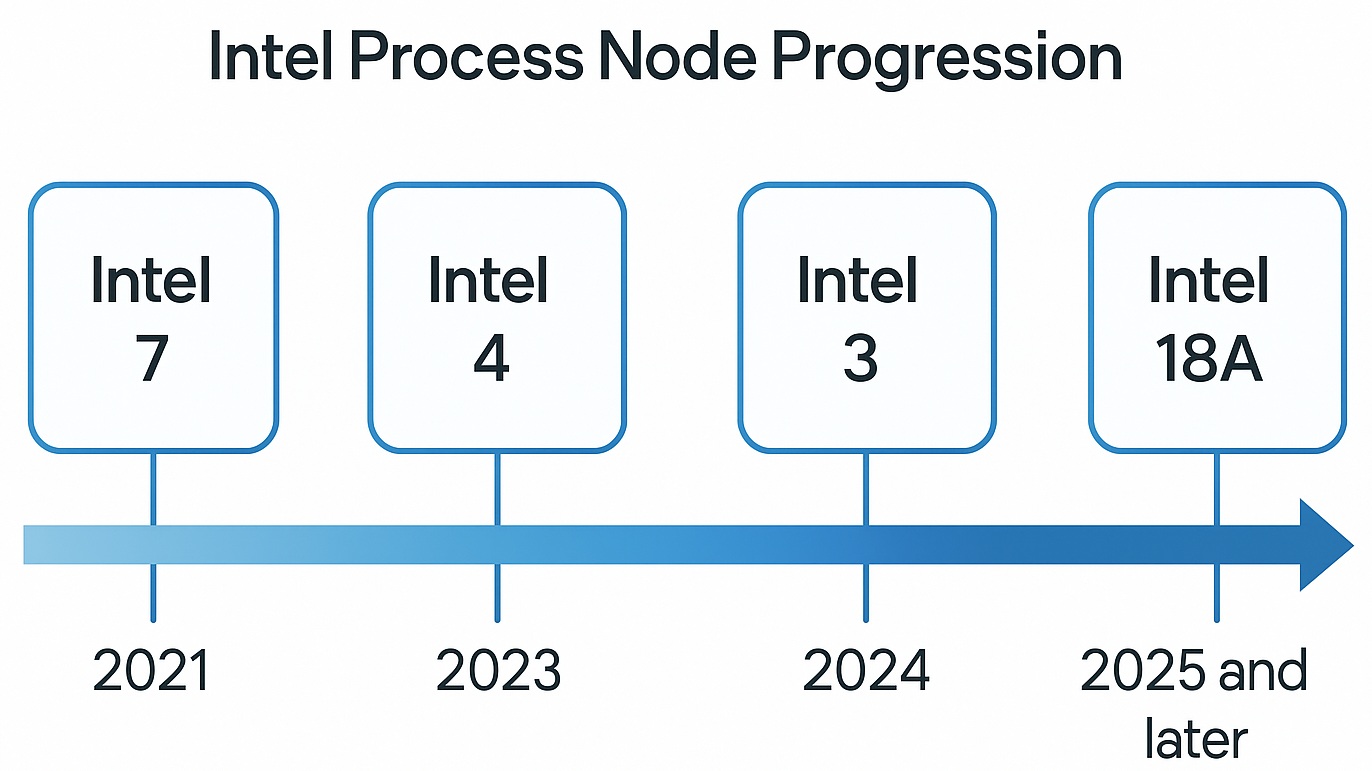

Timeline and Adoption

| Year | Intel 3 | Intel 18A |

|---|---|---|

| 2022 | Risk production | RibbonFET & PowerVia test chips shown |

| 2023 | Volume ramp for Sierra Forest, Granite Rapids | Pre-production of test SoCs |

| 2024 | HVM in Intel servers | Internal SoCs (e.g., Clearwater Forest) |

| 2025 | Select foundry customer ramp | Commercial availability via Intel Foundry Services (IFS) |

Strategic Significance

-

Intel 3 is the final FinFET node, extending the life of mature tools and enabling continuity before the GAA transition.

-

Intel 18A is the cornerstone of Intel’s IDM 2.0 and IFS strategy, showcasing both design leadership and foundry competitiveness.

-

Intel 18A is designed to be foundry-first, with full support for external fabless customers and chiplet ecosystems (UCIe).

Looking Ahead

| Intel Node | Transistor | Power Delivery | High-NA EUV |

|---|---|---|---|

| Intel 3 | FinFET | Front-side | No |

| Intel 18A | RibbonFET | PowerVia | No (yet) |

| Post-18A (14A or 10A?) | RibbonFET+, Forksheet | TBD | High-NA possible |

Summary Table

| Attribute | Intel 3 | Intel 18A |

|---|---|---|

| Node Class | 7nm-class | 1.8nm-class (advanced) |

| Transistor | FinFET | RibbonFET (GAAFET) |

| Backside Power | ❌ | ✅ PowerVia |

| PPA Gain (vs prior) | ~+18% perf / –18% power | +10–15% perf / –25–30% power |

| Availability | 2023–2024 | 2025 (internal), 2025+ (external) |

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry