Up to now the RISC-V community has been developing open-source processor implementations to a stage where they can appeal to system designers looking for alternatives to proprietary Arm and x86 cores. Toward this end, two projects have emerged as particularly significant examples of where RISC-V is heading. One is Ara, a vector… Read More

Tag: XiangShan

What XiangShan Got Right—And What It Didn’t Dare Try

An Open ISA, a Closed Mindset — Predictive Execution Charts a New Path

The RISC-V revolution was never just about open instruction sets. It was a rare opportunity to break free from the legacy assumptions embedded in every generation of CPU design. For decades, architectural decisions have been constrained by proprietary patents,… Read More

An Open-Source Approach to Developing a RISC-V Chip with XiangShan and Mulan PSL v2

As RISC-V gains traction in the global semiconductor industry, developers are exploring fully open-source approaches to processor design. XiangShan, a high-performance RISC-V CPU project, combined with the Mulan Permissive License v2 (Mulan PSL v2), represents a community-driven, transparent alternative to proprietary… Read More

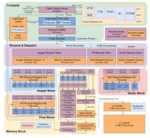

S2C’s FPGA Prototyping Accelerates the Iteration of XiangShan RISC-V Processor

S2C announced that the Beijing Institute of Open Source Chip (BOSC) adopted its Prodigy S7-19P Logic System, a VU19P-based FPGA prototyping solution, in the development of the “XiangShan” RISC-V processor. S7-19P not only accelerates the iterations of processor development but also simplifies other companies to realize … Read More