The dominance of GPUs in AI workloads has long been driven by their ability to handle massive parallelism, but this advantage comes at the cost of high-power consumption and architectural rigidity. A new approach, leveraging a chiplet-based RISC-V vector processor, offers an alternative that balances performance, efficiency,… Read More

Tag: UCIe

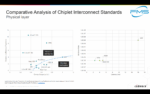

Will 50% of New High Performance Computing (HPC) Chip Designs be Multi-Die in 2025?

Predictions in technology adoption often hinge on a delicate balance between technical feasibility and market dynamics. While business considerations play a pivotal role, the technical category reasons for the success or failure of a prediction are more tangible and often easier to identify—if scrutinized with care. However,… Read More

Scaling AI Data Centers: The Role of Chiplets and Connectivity

Artificial intelligence (AI) has revolutionized data center infrastructure, requiring a reimagining of computational, memory, and connectivity technologies. Meeting the increasing demand for high performance and efficiency in AI workloads has led to the emergence of innovative solutions, including chiplets, advanced… Read More

Synopsys and TSMC Pave the Path for Trillion-Transistor AI and Multi-Die Chip Design

Synopsys made significant announcements during the recent TSMC OIP Ecosystem Forum, showcasing a range of cutting-edge solutions designed to address the growing complexities in semiconductor design. With a strong emphasis on enabling next-generation chip architectures, Synopsys introduced both new technologies and … Read More

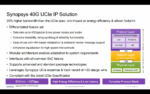

Synopsys Powers World’s Fastest UCIe-Based Multi-Die Designs with New IP Operating at 40 Gbps

As the demand for higher performance computing solutions grows, so does the need for faster, more efficient data communication between components in complex multi-die system-on-chip (SoC) designs. In response to these needs, Synopsys has introduced the world’s fastest UCIe-based IP solution, capable of operating at a groundbreaking… Read More

CEO Interview: Wendy Chen of MSquare Technology

Wendy Chen, MBA from the University of Manchester, has been the Founder and CEO of MSquare Technology since 2021. With over 23 years in the semiconductor industry, Wendy’s career includes roles as Sales Director at Synopsys Technology, Vice President at TF-AMD, and Vice President at Alchip Asia Pacific. Her extensive experience… Read More

The Impact of UCIe on Chiplet Design: Lowering Barriers and Driving Innovation

The semiconductor industry is experiencing a significant transformation with the advent of chiplet design, a modular approach that breaks down complex chips into smaller, functional blocks called chiplets. A chiplet-based design approach offers numerous advantages, such as improved performance, reduced development … Read More

Blue Cheetah Advancing Chiplet Interconnectivity #61DAC

At #61DAC, I love it when an exhibitor booth uses a descriptive tagline to explain what they do, like when the Blue Cheetah booth displayed Advancing Chiplet Interconnectivity. Immediately, I knew that they were an IP provider focusing on chiplets. I learned what sets them apart is how customizable their IP is to support specific… Read More

Siemens Provides a Complete 3D IC Solution with Innovator3D IC

Heterogeneous multi-die integration is gaining more momentum all the time. The limited roadmap offered by Moore’s Law monolithic, single-die integration has opened the door to a new era of more-than-Moore heterogeneous integration. The prospects offered by this new design paradigm are exciting and the entire ecosystem is… Read More

Mirabilis Design at the 2024 Design Automation Conference

This is the first time in 28 years of my visits to DAC that I have seen so many different technologies arrive at DAC in the same year. Earlier we would have one or possibly two innovative breakthroughs in semiconductors and embedded systems that emerged at DAC. This year I expect six or may be seven to arrive, and I am not including the… Read More