Given the success of the event in Silicon Valley last week, I would expect the Siemens U2U event in Munich to be even bigger. In my experience this has been the best user driven event in 2026 with the deepest customer content. EDA has always been a customer driven industry and it is good to see us recognize that from time to time. Kalar … Read More

Tag: UCIe

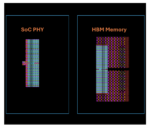

Scaling Multi-Die Connectivity: Automated Routing for High-Speed Interfaces

This article concludes the three-part series examining key methodologies required for successful multi-die design. The first article Reducing Risk Early: Multi-Die Design Feasibility Exploration focused on feasibility exploration and early architectural validation, while the second article Building the Interconnect… Read More

Podcast EP335: The Far Reaching Impact of UCIe with Dr. Debendra Das Sharma

Daniel is joined by Dr. Debendra Das Sharma, a Senior Fellow and Chief I/O architect in the Data Platforms and Artificial Intelligence Group at Intel. He is a member of the National Academy of Engineering (NAE), Fellow of IEEE, and Fellow of International Academy of AI Sciences. He is a leading expert on I/O subsystem and interface… Read More

Keynote: On-Package Chiplet Innovations with UCIe

In the rapidly evolving landscape of semiconductor technology, the Universal Chiplet Interconnect Express (UCIe) emerges as a groundbreaking open standard designed to revolutionize on-package chiplet integrations. Presented by Dr. Debendra Das Sharma, Chair of the UCIe Consortium and Intel Senior Fellow, at the Chiplet… Read More

TSMC and Cadence Strengthen Partnership to Enable Next-Generation AI and HPC Silicon

TSMC continues to reinforce its leadership in advanced semiconductor manufacturing through its deepening collaboration with Cadence Design Systems. The expanded partnership focuses on enabling next-generation artificial intelligence and high-performance computing innovations by aligning advanced electronic design… Read More

Podcast EP329: How Marvell is Addressing the Power Problem for Advanced Data Centers with Mark Kuemerle

Daniel is joined by Mark Kuemerle, Vice President of Technology, Custom Cloud Solutions at Marvell. Mark is responsible for defining leading-edge ASIC offerings and architects system-level solutions. Before joining Marvell, Mark was a Fellow in Integrated Systems Architecture at GLOBALFOUNDRIES and has held multiple engineering… Read More

Revitalizing Semiconductor StartUps

Tarun Verma, Managing Partner of Silicon Catalyst, delivered a keynote at Verification Futures Austin titled “Revitalizing Semiconductor StartUps.” Drawing from his role in the world’s only accelerator focused on the global semiconductor industry, Tarun outlined the sector’s resurgence, persistent… Read More

Chiplets: Powering the Next Generation of AI Systems

AI’s rapid expansion is reshaping semiconductor design. The compute and I/O needs of modern AI workloads have outgrown what traditional SoC scaling can deliver. As monolithic dies approach reticle limits, yields drop and costs rise, while analog and I/O circuits gain little from moving to advanced process nodes. To sustain … Read More

Advancing Semiconductor Design: Intel’s Foveros 2.5D Packaging Technology

In the rapidly evolving landscape of semiconductor manufacturing, the demand for processors that handle increasing workloads while maintaining power efficiency and compact form factors has never been higher. Intel’s Foveros 2.5D packaging technology emerges as a pivotal innovation, enabling denser die integration… Read More

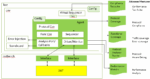

Smart Verification for Complex UCIe Multi-Die Architectures

By Ujjwal Negi – Siemens EDA

Multi-die architectures are redefining the limits of chip performance and scalability through the integration of multiple dies into a single package to deliver unprecedented computing power, flexibility, and efficiency. At the heart of this transformation is the Universal Chiplet Interconnect… Read More