The semiconductor industry is experiencing unprecedented growth in complexity as advanced process nodes, heterogeneous integration, and AI-driven workloads demand increasingly sophisticated chip designs. At the same time, semiconductor companies face rising design costs, increasing engineering workloads, and a shrinking… Read More

Tag: tessent

Siemens Describes its System-Level Prototyping and Planning Cockpit

We all know semiconductor design is getting harder. Much harder when you consider the demands of AI workloads and heterogeneous integration of many chiplets in a single package. This class of system demands co-optimization across the entire design flow. For example, functional verification, thermal analysis, signal and power… Read More

New Product for In-System Test

The annual ITC event is happening this week in San Diego as semiconductor test professionals gather from around the world to discuss their emerging challenges and new approaches, so last week I had the opportunity to get an advance look at something new from Siemens named Tessent In-System Test software. Jeff Mayer, Product Manager,… Read More

AI-Powered Transformation in EDA

The integration of artificial intelligence (AI) into Electronic Design Automation (EDA) is revolutionizing chip design, addressing the critical shortage of skilled engineers and accelerating the development process. As Jeff Dyck, Senior Director of Engineering at Siemens EDA, explains in a recent DACtv presentation, … Read More

Podcast EP232: The Evolution of Yield Learning and Silicon Debug with Marc Hutner

Dan is joined by Marc Hutner. Marc has been innovating in the areas of design, test, DFT and data analytics for more than 20 years. In June of 2023, he joined the Siemens EDA Tessent group as the product director of Silicon Learning, enabling how silicon data is applied to yield improvement and silicon debug. Previously, he worked … Read More

Three New Circuit Simulators from Siemens EDA

The week before DAC I had the privilege to take a video call with Pradeep Thiagarajan – Product Manager, Simulation, Custom IC Verification at Siemens EDA to get an update on new simulation products. I’ve been following Solido for years now and knew that they were an early adopter of ML for Monte Carlo simulations with SPICE users.… Read More

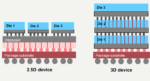

DFT Moves up to 2.5D and 3D IC

The annual ITC event was held the last week of September, and I kept reading all of the news highlights from the EDA vendors, as the time spent on the tester can be a major cost and the value to catching defective chips from reaching production is so critical. Chiplets, 2.5D and 3D IC design have caught the attention of the test world, … Read More

Efficient Memory BIST Implementation

Test experts use the acronym BIST for Built In Self Test, it’s the test logic added to an IP block that speeds up the task of testing by creating stimulus and then looking at the output results. Memory IP is a popular category for SoC designers, as modern chips include multiple memory blocks for fast, local data and register storage… Read More

Balancing Test Requirements with SOC Security

Typically, there is an existential rift between the on-chip access requirements for test and the need for security in SoCs. Using traditional deterministic scan techniques has meant opening up full read and write access to the flops in a design through the scan chains. Having this kind of access easily defeats the best designed… Read More

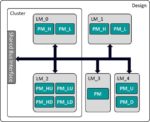

Tessent Streaming Scan Network Brings Hierarchical Scan Test into the Modern Age

Remember when you had to use dial up internet or parallel printer cables connected directly to the printer to print something? Well even if you don’t remember these things, you know that now there is a better way. Regrettably, the prevalent methods used for hierarchical Design for Test (DFT) still look at lot like this – SoC level … Read More