Agnisys Inc. a leader in design and verification automation for hardware development, is gearing up for an impactful presence at DAC 2024. This year’s participation will be marked by various activities designed to engage and inspire the electronic design automation (EDA) community. Attendees can look forward to our … Read More

Tag: systemc

Something new in High Level Synthesis and High Level Verification

As SoC complexities continue to expand to billions of transistors, the quest for higher levels of design automation also rises. This has led to the adoption of High-Level Synthesis (HLS), using design languages such as C++ and SystemC, which is more productive than traditional RTL design entry methods. In the RTL approach there… Read More

CEO Interview: Dr. Nasib Naser of ORION VLSI Technologies.

Dr. Nasib Naser brings over 35 years of experience in the field. His expertise spans the entire VLSI cycle from conception to chip design, with a strong focus on verification methodologies. For his 17 years at Synopsys, Dr. Naser have held senior management positions, leading North American Verification IP, managing Central … Read More

WEBINAR: How to Achieve 95%+ Accurate Power Measurement During Architecture Exploration

Today’s power modeling solutions are trained at measuring power using the micro-events captured from detailed RTL simulation or studying the electromagnetic radiation from IR drop and side channel attacks. These solutions are fantastic for debugging and verification of the implementation. There are both open source and … Read More

The Inconvenient Truth of Clock Domain Crossings

Almost everything that we do in chip design and verification was invented to raise the abstraction above schematics and polygons. Register-transfer-level (RTL) design, functional simulation, logic synthesis, floorplanning, and more fall into this category. Even the notion of binary circuits is an abstraction. Underneath… Read More

AMIQ: Celebrating 20 Years in Consulting and EDA

We’re getting close to the annual July Design Automation Conference (DAC) in San Francisco, and every year I like to make the rounds of the exhibitors beforehand and see what’s new. When I checked with AMIQ EDA, I found that this is a big year for them. Their parent company AMIQ just reached its 20th anniversary, and they’ll be celebrating… Read More

The State of IC and ASIC Functional Verification

Way back in 2002 there was a study from Collett International Research on functional verification, and since 2010 the Wilson Research Group has continued that same kind of study with a new report every two years. What attracts me to this report is that it doesn’t just look at the installed base of one EDA vendor, instead it looks… Read More

Rethinking the System Design Process

The system design process can incorporate linear thinking, parallel thinking, or both, depending on the nature of the anticipated system, subsystem, or element of a subsystem. The structure, composition, scale, or focal point of a new/incremental system design incorporates the talents and gifts of the designer in either a … Read More

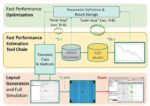

Automating and Optimizing an ADC with Layout Generators

I first got involved with layout generators back in 1982 while at Intel, and about 10% of a GPU was automatically generated using some code that I wrote. It was an easy task for one engineer to complete, because the circuits were digital, and no optimization was required. In an IEEE paper from the 2022 18th International Conference… Read More

SoC Application Usecase Capture For System Architecture Exploration

Sondrel is the trusted partner of choice for handling every stage of an IC’s creation. Its award-winning define and design ASIC consulting capability is fully complemented by its turnkey services to transform designs into tested, volume-packaged silicon chips. This single point of contact for the entire supply chain… Read More