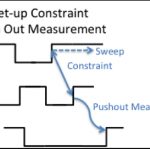

During synthesis and static timing the main figure of merit is “slack”. If a signal arrives with time to spare before it is needed (often measured against the setup time before a clock changes at a register) then the slack is positive. Positive slack is generally a good thing, although it can indicate over-design if … Read More

Tag: static timing

Antun Domic, on Synopsys’ Secret Sauce in Design

Antun Domic is the GM of the Design Group at Synopsys. I sat down with him a couple of weeks ago.

His name is Croatian although, of course, there was no Croatia back then it was part of Yugoslavia. But in fact he grew up in Chile and went to university there where he studied EE and math. He came to the US as a grad student and did a PhD at MIT in … Read More

FinFET: The Miller’s Tale

In Chaucer’s Canterbury Tales, the second of the tales told by the pilgrims is The Miller’s Tale. Since this is a family blog, I’ll leave you to research the tale yourself. But FinFETs hide another Miller’s Tale, due to Miller capacitance, sometimes called the Miller effect. This is significant since in FinFET designs Miller capacitance… Read More

Tempus: Cadence Takes On PrimeTime

Today Cadence announced Tempus, their new timing signoff solution. This has been in development for at least a couple of years and has been built from the ground up to be massively parallelized. Not just that different corners can be run in parallel (which is basically straightforward) but that large designs can be partitioned … Read More

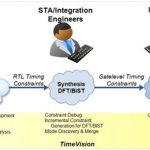

Ausdia’s Timevision

I met Sam Appleton of Ausdia during DAC. I found it quite hard to understand exactly what they do. I’ve talked before about something that I nick-named City Slickers’ Marketing. It is named after the following exchange from the movie City Slickers:Curly: Do you know what the secret of life is? [holds up one finger] This.… Read More