Variation analysis continues to be increasingly important as process technology moves to more advanced nodes. It comes as no surprise that tool development in this area has been vigorous and aggressive. New higher reliability IC applications, larger memory sizes and much higher production volumes require sophisticated yield… Read More

Tag: standard cell

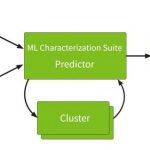

Machine Learning Accelerates Library Characterization by 50 Percent!

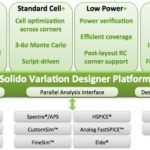

Standard cell, memory, and I/O library characterization is a necessary, but time-consuming, resource intensive, and error-prone process. With the added complexity of advanced and low power manufacturing processes, fast and accurate statistical and non-statistical characterization is challenging, creating the need … Read More

Webinar Offers View into TSMC IP Design Methodology

Standard cell and memory IP are key enablers for new process node availability. These two items must be in place early and be completely ready for a process node to scale to volume. Development of both leaves no room for error and they require the highest performance possible. Foundries are extremely focused on this and spend a lot… Read More

TSMC and Solido to Share Experiences with Managing Variation in Webinar

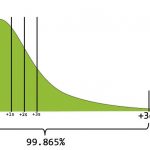

TSMC knows better than anyone the effect that variation can have at advanced process nodes. Particularly in memory designs and in standard cell designs, variation has become a very critical because of its effects on yield and because of the high-cost of compensating for it. Smaller feature sizes combined with lower voltage thresholds… Read More

How TSMC Tackles Variation at Advanced Nodes

The design community is always hungry for high-performance, low-power, and low-cost devices. There is emergence of FinFET and FDSOI technologies at ultra-low process nodes to provide high-performance and low-power requirements at lower die-size. However, these advanced process nodes are prone to new sources of variation.… Read More

Standard Cell, IO and Hard IP Validation update

Every SoC team uses libraries of cells to get their new product to market quicker: Standard Cells, IO Cells and Hard IP blocks. One immediate question that comes to my mind is, “How clean are these cells?” Validating your cell libraries first makes sense, and will ensure that there are fewer surprises as your chip gets… Read More

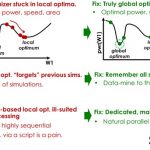

High-Sigma Standard Cell Optimization!

Standard cell optimization is an important problem, because the speed, power, and area of cells has a direct impact speed, power, and area of the whole chip. Typically, standard cell optimization been done with simple in-house local-optimizer scripts. However, these optimizers have had several flaws: they don’t properly capture… Read More

Validating Hard IP & Std Cell Libraries at DAC

The building blocks for every SoC are standard cell libraries that are assembled, designed and verified together. But how do we really know if all the data formats used during design are correct and consistent? To answer that question I spoke with Johan Peetersof Fractal Technologiesat DAC.

Johan Peeters, Rene Donkers

… Read More