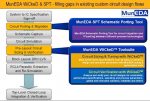

The commonly advanced reason for IP reuse is lower cost and shorter development time. However, IP reuse presents its own challenges, especially for analog designs. In the case of digital designs, once a new standard cell library is available, it is usually not too hard to resynthesize RTL to create new working silicon. For analog… Read More

Tag: spice simulation

Solido Saves Silicon with Six Sigma Simulation

When pushing the boundaries of power and performance in leading edge memory designs, yield is always an issue. The only way to ensure that memory chips will yield is through aggressive simulation, especially at process corners to predict the effects of variation. In a recent video posted on the Solido website, John Barth of Invecas… Read More

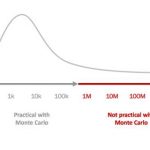

Replacing the British Museum Algorithm

In principle, one way to address variation is to do simulations at lots of PVT corners. In practice, most of this simulation is wasted since it adds no new information, and even so, important corners will get missed. This is what Sifuei Ku of Microsemi calls the British Museum Algorithm. You walk everywhere. And if you don’t walk to… Read More