Design for test (DFT) imposes various restrictions on the design so that the test automation tools (automatic test pattern approaches such as scan, as well as built-in self-test approaches) will subsequently be able to generate the test program. For example, different test approaches impose constraints on clock generation… Read More

Tag: soc realization

SOC Realization

There are some very interesting comments to the last entry on SoC Realization and how more and more chips are actually assembled out of IP. There was clearly a lot of discussion in this area at DAC, although most people (Atrenta being an exception) don’t use the term SoC Realization, presumably because it was originated by … Read More

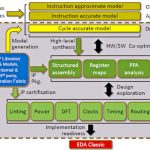

SOC Realization: How Chips Are Really Designed

If you just casually peruse most marketing presentations by EDA companies, you’d come to the conclusion most SoCs are designed from scratch, wrestlilng the monster to the ground with bare hands. But the reality is that most SoCs consist of perhaps 90% IP blocks (many of them memories). That still leaves the remaining 10% … Read More