DAC has several “Insight Presentations” on Wednesday June 5th. Bryan Bowyer from Calypto will be presenting from 2-4pm that day (don’t know where, the DAC website doesn’t have a room number specified yet). The topic is Reducing Design and Debug Time with Synthesizable TLM. TLM, of course, stands for… Read More

Tag: semiconductor

DAC Keynotes: 5 This Year

DAC is in Austin this year, as I’m sure you know, and DAC has keynotes by CEOs of two Austin-based companies Freescale Semiconductor and National Instrument. Two more keynotes (one split into two) are focused on mobile, which has become the major driver of semiconductor today. A fifth keynote, including presentation of … Read More

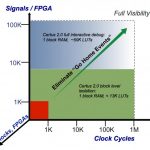

Accelerating Design Debug in an ASIC Prototype

ASIC prototyping in FPGAs is starting to trend on SemiWiki. As FPGA technology becomes more advanced customers tell me that the traditional debug tools are inadequate. Faced with the very restrictive debugging capabilities and very long synthesis/place/route times the debugging cycle in these prototype platforms are quite… Read More

Crossfire – Builds Quality with Design

Very often we talk about increasing design complexities and verification challenges of SoCs. With ever growing design sizes and multiple IPs on a single SoC, it’s a fact that SoC design has become heterogeneous, being developed by multiple teams, either in-house or outsourced. Considering economic advantage amid pressure … Read More

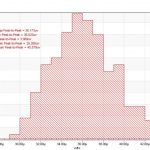

Recovery in 2013 Semiconductor Capex

Semiconductor manufacturing equipment has been on an upswing for the last few months. Combined data from Semiconductor Equipment and Materials International (SEMI) and Semiconductor Equipment Association of Japan (SEAJ) shows three-month-average bookings have increased for five consecutive months through March 2013.… Read More

Hot Topic – CMOS Image Sensor Verification!

Mobile applications require CMOS image sensor devices that have a low signal-to-noise ratio (SNR), low power, small area, high resolution, high dynamic range, and high frame rate. CMOS image sensor imaging performance is noise limited requiring accurate noise analysis on the pixel array electronics and column readout circuitry.… Read More

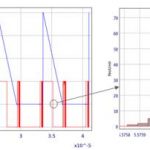

Transient Noise Analysis (TNA)

Tanner EDA Applications Engineers see a broad range of technical challenges that our users are trying to overcome. Here’s one worth sharing – it deals with transient noise analysis (TNA) for a comparator design. The customer is a producer of advanced flow measurement devices for application in medicine and research. The designer… Read More

MOS-AK/GSA Munich Workshop

The MOS-AK/GSA Modeling Working Group, a global compact modeling standardization forum, completed its annual spring compact modeling workshop on April 11-12, 2013 at the Institute for Technical Electronics, TUM, Munich. The event received full sponsorship from leading industrial partners including MunEDA and Tanner EDA.… Read More

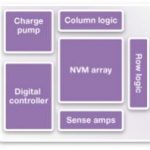

NVM IP Security Solutions…

If you need securely storing in your SoC a data which is by nature unique, like encryption key, or a software code update, then you will probably decide to implement a Non Volatile Memory (NVM) block, delivered as an IP function, instead of using an expensive CMOS technology with embedded Flash capability. For example, Synopsys … Read More

Reduce Errors in Multi-threaded Designs

Many advanced algorithmic IPs are described in C++. We use this language because of its flexibility. Of course software algorithms are written to be executed on processors so they don’t solve all the issues of getting the algorithm implemented in hardware directly. This is not simply a high-level synthesis (HLS) issue. Usually… Read More