Integrated wafer-level fanout (WLFO) packaging technology is emerging as a foundation for multi-die solutions. Mobile product applications require focus on both aggressive chip-to-chip interface performance, as well as the final package volume. Traditional multi-chip packages using PCB laminate substrates do not readily… Read More

Tag: pop

ARM Seahawk

I wrote on Monday about ARM’s Processor Optimization Packs (POPs). In Japan they announced yesterday the Seahawk hard macro implementation in the TSMC 28HPM process. It is the highest performance ARM to date, running at over 2GHz. It is a quad-core Cortex A15.

The hard macro was developed using ARM Artisan 12-track libraries… Read More

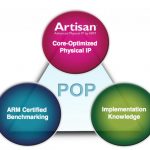

Making your ARMs POP

Just in time for TSMC’s technology symposium (tomorrow) ARM have announced a whole portfolio of new Processor Optimization Packs (POPs) for TSMC 40nm and 28nm. For most people, me included, my first question was ‘What is a POP?’

A POP is three things:

- physical IP

- certified benchmarking

- implementation knowledge