The global Interface IP market is still growing in 2015, no doubt about it. It’s interesting to zoom in the various protocols to check their respective behavior. Which protocol generates an IP business growing more than the average market? Which protocol generates a disappointing IP business? In other words, which are the winners… Read More

Tag: phy

Synopsys Vision on Custom Automation with FinFET

In an overwhelmingly digital world, there is a constant cry about the analog design process being slow, not automated, going at its own pace in the same old fashion, and so on. And, the analog world is not happy with the way it’s getting dragged into imperfect automation so it can be more like the digital world. True, the analog world… Read More

Does Multiprotocol-PHY IP really boost TTM?

I have often written in Semiwiki about high speed PHY IP supporting Interface protocols (see for example this blog), the SoC cornerstone, almost as crucial as CPU, GPU or SDRAM Memory Controller. When you architect a SoC, you first select CPU(s) and/or GPU(s) to support the system basic functionality (Processor for Mobile application,… Read More

AMS IC Design at SilabTech

Through my contacts at SemiWiki I was introduced to a mixed signal IP company named SilabTech, and then decided to interview the founder and CEO, Sujoy Chakravarty.

Sujoy Chakravarty, CEO and Founder

… Read More

Should You Buy All Aspects of Your IP From a Single Supplier?

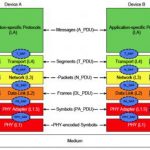

Interface IP typically consists of multiple layers, most importantly a PHY (level 1) analog (or mixed signal) block that handles the interface to the outside world and a number of levels of digital controllers. The interfaces between all these levels, especially between the PHY and the controller, is often defined by the interface… Read More

Such a small piece of Silicon, so strategic PHY IP

How could I talk about the various Interface protocols (PCIe, USB, MIPI, DDRn…) from an IP perspective and miss the PHY IP! Especially these days, where the PHY IP market has been seriously shaken, as we will see in this post, and will probably continue to be shaken… but we will have to wait and look at the M&A news during the next … Read More