You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Veriest recently hosted a webinar focusing on RISC-V as a forerunner of ongoing open-source revolution in chip design. Speakers were distinguished professionals from industry and academia. Webinar covered topics from market trends to open-source hardware initiatives, tools and methodologies.

Zvonimir Bandić: RISC-V … Read More

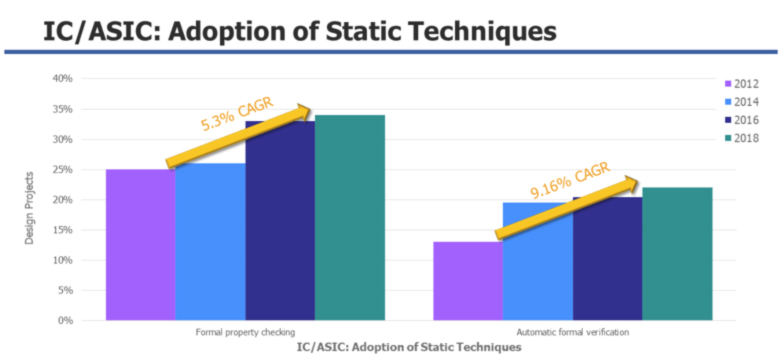

After a few decades of watching formal verification techniques being applied to SoC designs, it certainly continues to be a growth market for EDA vendors. In the first decades from 1970-1990 the earliest forms of formal tools emerged at technical conferences, typically written by University students earning their Ph.D.s, … Read More

Connecting the Divide between Design and Manufacturing is an overarching theme within the ESD Alliance as these two essential semiconductor disciples become more reliant on each other. It’s also the reason we’re hosting SMART Design, the first system-centric series showcasing advances in electronic system design to be held… Read More

IC Integrity Thesisby Jim Hogan on 04-09-2019 at 12:00 pmCategories: EDA, Onespin, RISC-V

Most of my investments are associated with large changes in the semiconductor industry. These changes create opportunities for new and disruptive technologies. I also look to find solutions that provide a compelling reason to adopt a new technology or approach. When talking about a new approach, it often takes longer to overcome… Read More

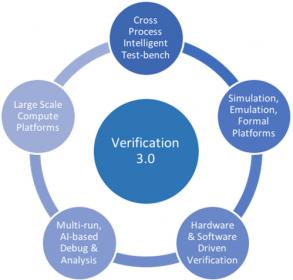

Last week I attended the first Verification 3.0 Innovation Summit held at Levi’s Stadium in Santa Clara along with about 90 other interested engineers and former engineers (meaning marketing and sales people, like me). There was a great vibe and feel to the event as it exuded an energy level that I have not felt at an EDA event in years.… Read More

Welcome to my newly relocated column, I am so excited about my new relationship with Daniel Nenni, and the other esteemed bloggers on SemiWiki. For those who do not know me, I have been a featured columnist on another EDA portal for the past 12-plus years, and in EDA for 20-plus years. As the leading recruiter in our industry, (or so … Read More

I love getting a good deal, and free is always compelling, so how about attending DAC in Austin for free this year? Sound too good to be true? Thanks to the generosity of three EDA companies – ATop Tech, ClioSoft and OneSpin, now you can can attend parts of DAC for free by registering here. This is now the 8th year that the I LOVE DAC… Read More

Formal verification is qualitatively different from most other verification. A simulation can pass or fail. But while formal verification can prove that the circuit is correct, or incorrect, it can also return “not proven” which means either that the algorithms realized that they were not powerful enough to prove… Read More

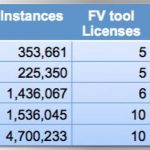

Formal verification can be used for many things, but one is to ensure that synthesis performs correctly and that the behavior of the output netlist is the same as the behavior of the input RTL. But designs are getting very large and formal verification is a complex tool to use, especially if the design is too large for the formal tool… Read More