The MOS-AK/GSA Modeling Working Group, a global compact modeling standardization forum, completed its annual spring compact modeling workshop on April 11-12, 2013 at the Institute for Technical Electronics, TUM, Munich. The event received full sponsorship from leading industrial partners including MunEDA and Tanner EDA.… Read More

Tag: muneda

Robustness, Reliability and Yield at DAC

On Wednesday at DAC I met with Bob Slee, distributor and Michael Siu, AE for MunEDA to get an update on what’s new. MunEDA has EDA software for:

- Schematic porting

- Nominal circuit analysis

- Nominal circuit optimization

- Statistical circuit analysis

- Statistical circuit optimization

- IP porting

- Circuit model generation

Magma FineSIM and MunEDA Cooperate

How do I know if an AMS block is tuned for the process and will perform and yield acceptably?… Read More

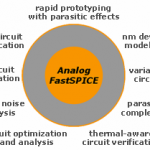

Nanometer Circuit Verification Forum

Verifying circuits on advanced process nodes has always been difficult, and it’s no easier with today’s nanometer CMOS processes. There’s a great paradox in nanometer circuit design and verification. Designers achieve their greatest differentiation when they implement analog, mixed-signal, RF and custom … Read More