I started designing ICs in 1978 and continued through 1986, and each chip used hierarchy and partitioning but our methodology was totally ad-hoc, and documented on paper, so it was time consuming to make revisions to the chip or train someone else on the history or our chip, let alone re-use any portion of our chips again. Those old,… Read More

Tag: methodics

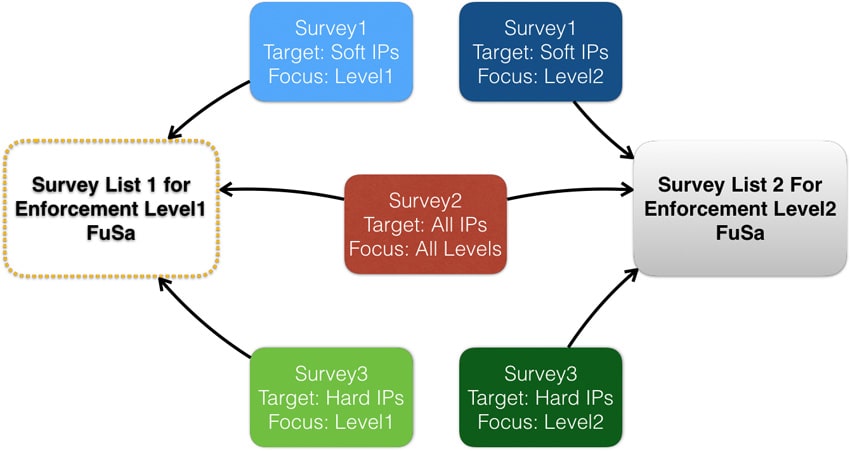

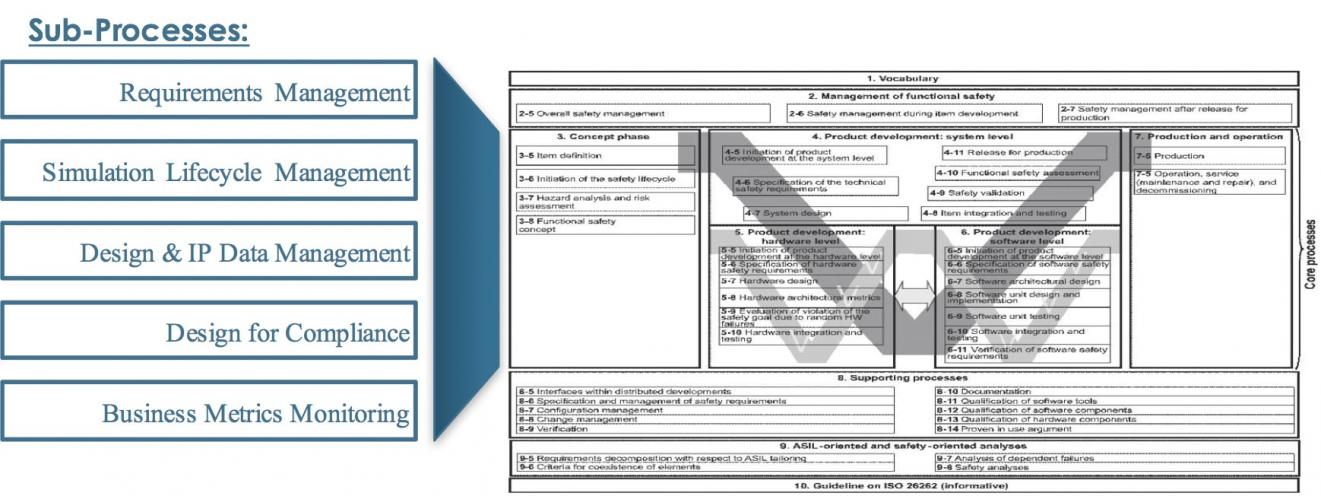

Using IP in a SoC Compliant with ISO 26262

The automotive segment is being well served by semiconductor suppliers of all sizes because of the unit volumes, and the constant push to automate more of the driving decisions to silicon and software can raise lots of questions about safety, reliability and trust. Fortunately the ISO standards body has already put in place a functional… Read More

IP Management Using both Git and Methodics

I use Quicken to manage my business and personal finances because it saves me so much time by downloading all of my transactions from Chase for credit card, Amazon for credit card, Wells Fargo for banking and Schwab for IRA. Likewise, for IP management in SoC design you want an app like Quicken that plays well with other tools that you… Read More

What to Expect from Methodics at DAC

I’ve been visiting DAC for decades now, at first as an EDA vendor and since 2004 as a freelance EDA consultant. There’s always a buzz about what’s new, semiconductor industry trends, who is getting acquired and the latest commercial EDA and IP offerings. There’s so much vying for my attention at DAC each… Read More

ISO 26262 Traceability Requirements for Automotive Electronics Design

Reading the many articles on SemiWiki and other publications we find experts talking about the automotive market, mostly because it’s in growth mode, has large volumes and vehicles consume more semiconductors every year. OK, that’s on the plus side, but what about functional safety for automotive electronics?… Read More

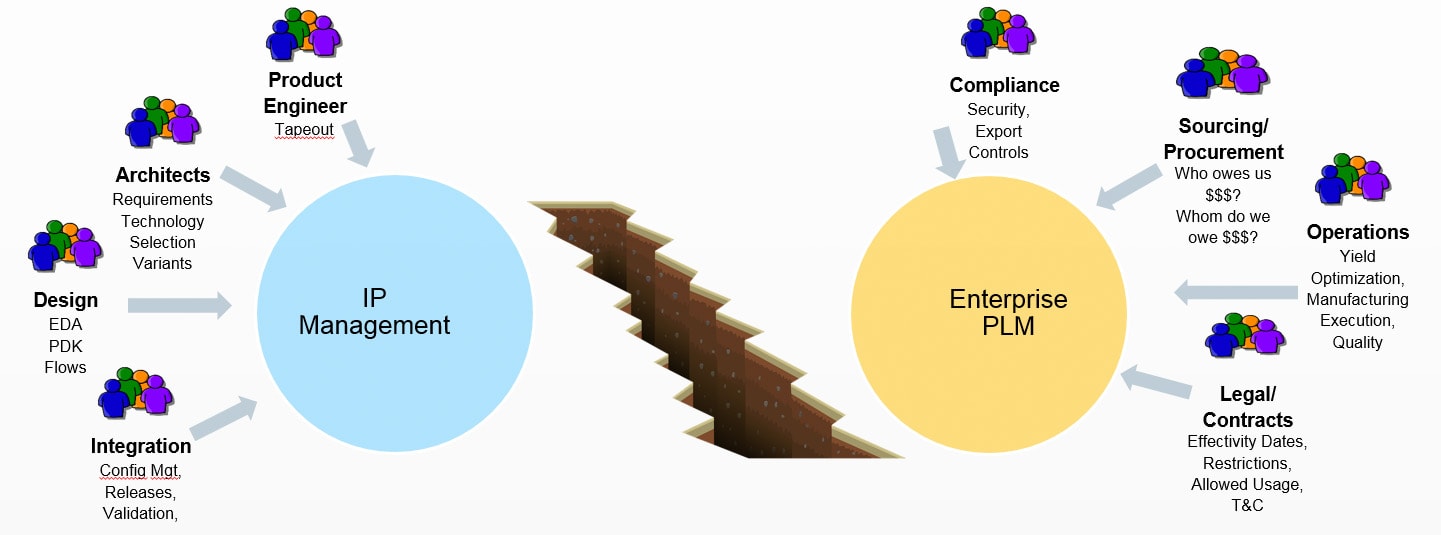

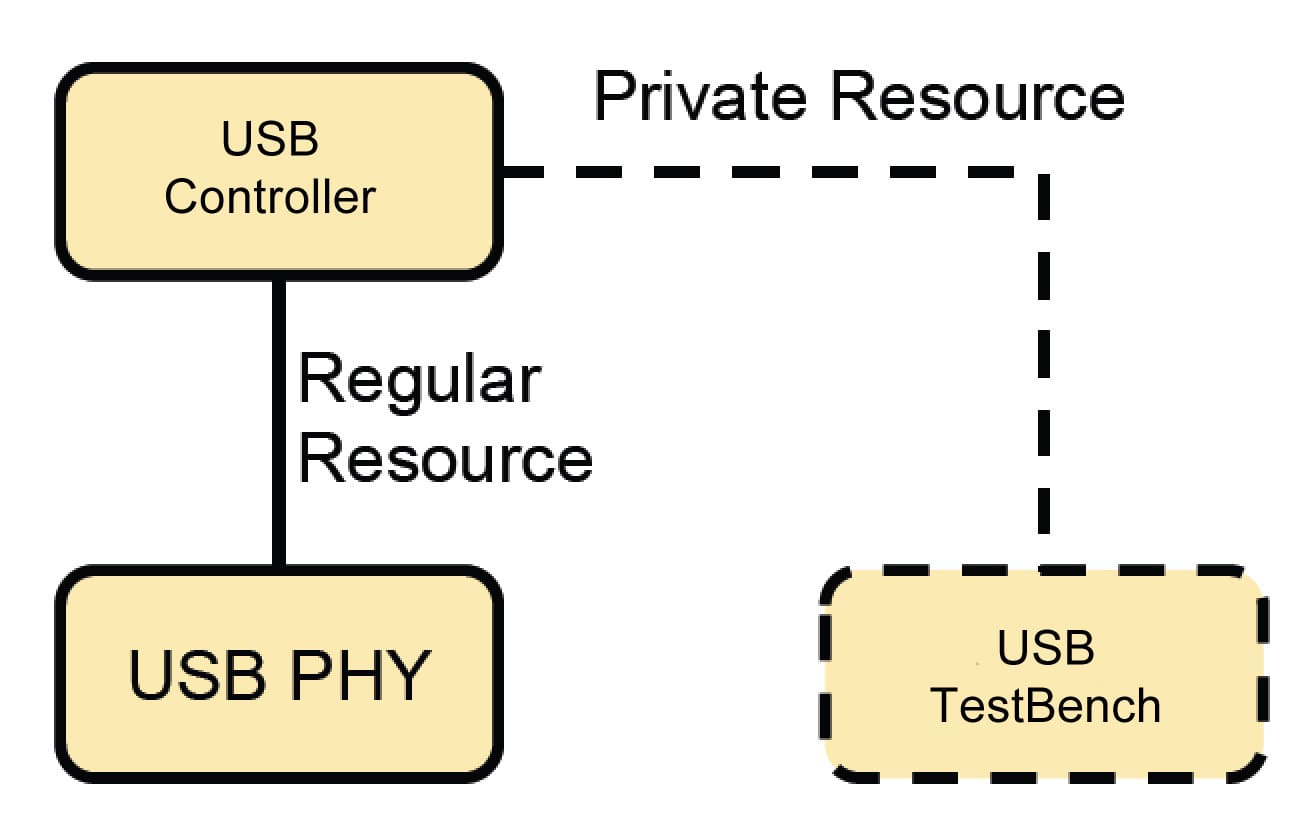

Combining IP and Product Lifecycle Tools

No single EDA company provides all of the tools needed to define requirements, design exploration, track IP, simulate, manage and verify a complex SoC system, so it makes sense that EDA vendors and point tool companies have tools that work together to achieve all of these difficult tasks. Systems design has been around for decades… Read More

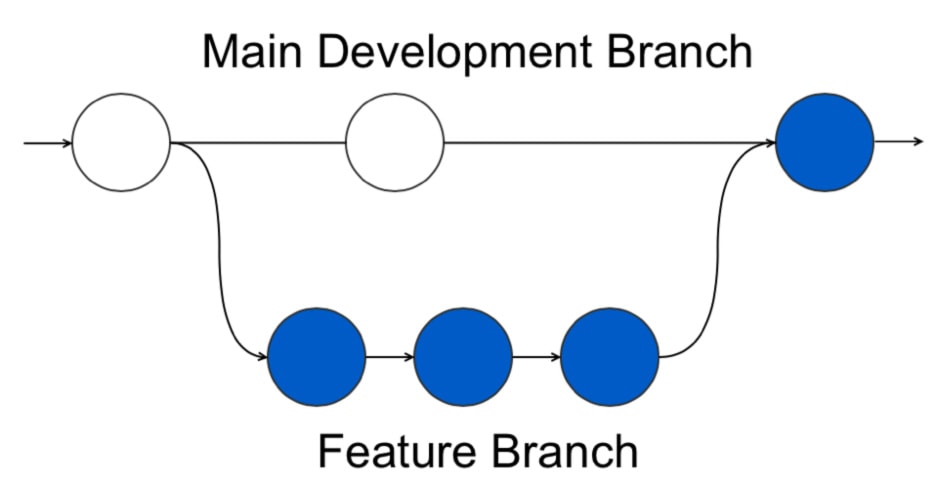

SoC Design Management with Git

Linux creator Linus Torvalds lives in Oregon not too far from me and he also created the popular Git system for Design Management (DM) in 2004 that is now used by many software developers. So what makes Git so attractive as a DM tool?

- Feature-branch workflow

- Easy to switch context between features

- New features can be created orderly

Hierarchy Applied to Semiconductor IP Reuse

When I first started doing IC design back in 1978 we had hierarchical designs, and that was doing a relatively simple 16Kb DRAM chip with only 32,000 transistors using 6um (aka 6,000 nm) design rules. SoC designs today make massive use of hierarchy at all levels of IC design: IC Layout, transistor netlist, gate level netlist, RTL … Read More

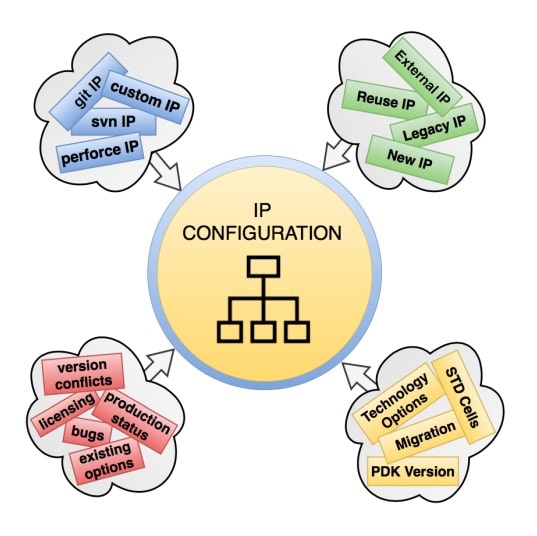

Rethinking IP Lifecycle Management

We recently saw both Apple and Samsung introduce new smart phones, and realize that the annual race to introduce sophisticated devices that are attractive and differentiated is highly competitive. If either of these companies misses a market window then fortunes can quickly change. SoCs with billions of transistors like smart… Read More

Something New in IP Lifecycle Management

Last month at DAC I met up with Michael Munsey of Methodics to get a quick update on what has been happening over the past 12 months within his company, and he quickly invited me to watch an archived webinar on their latest tool for IP Lifecycle Management called Percipient. I love to play the board game Scrabble, so i had to Google the … Read More