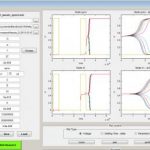

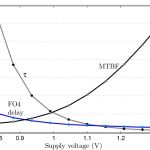

A webinar presented Last week introduced two free aids to evaluating synchronizer Mean Time Between Failures (MTBF). The first, MetaACE LTD, is used to characterize the intrinsic parameters needed to calculate MTBF (tau and Tw). This limited version of MetaACE supports up to 250 circuit nodes, which is enough for a typical C-only-extracted… Read More

Tag: metaace

Ten Ways Your Synchronizer MTBF May Be Wrong

Estimating the MTBF of an SoC should always include an analysis of synchronizer reliability. Contemporary process nodes are introducing new challenges to the reliability of clock domain crossings so it is prudent to revisit how your simulation tool calculates a synchronizer’s MTBF. Let’s list the ten most common pitfalls.… Read More

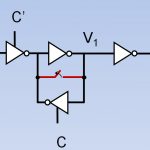

Metastability Starts With Standard Cells

Metastability is a critical SoC failure mode that occurs at the interface between clocked and clockless systems. It’s a risk that must be carefully managed as the industry moves to increasingly dense designs at 28nm and below. Blendics is an emerging technology company that I have been working with recently, their MetaACE… Read More

Metastability and Fatal System Errors

Metastability is an inescapable phenomenon in digital electronic systems. This phenomenon has been known to cause fatal system errors for half a century. Over the years, designers have used convenient rules of thumb for designing synchronizers to mitigate it. However, as digital circuits have become more complex, smaller … Read More