High-level synthesis (HLS) involves the generation of an RTL hardware model from a C/C++/SystemC description. The C code is typically referred to as abehavioraloralgorithmicmodel. The C language constructs and semantics available to architects enable efficient and concise coding – the code itself is smaller, easier to write/read,… Read More

Tag: lec

SmartScan Addresses Test Challenges of SoCs

With advancement of semiconductor technologies, ever increasing sizes of SoCs bank on higher densities of design rather than giving any leeway towards increasing chip area and package sizes; a phenomenon often overlooked. The result is – larger designs with lesser number of pins bonded out of ever shrinking package sizes;… Read More

Smart Clock Gating for Meaningful Power Saving

Since power has acquired a prime spot in SoCs catering to smart electronics performing multiple jobs at highest speed; the semiconductor design community is hard pressed to find various avenues to reduce power consumption without affecting functionality and performance. And most of the chips are driven by multiple clocks that… Read More

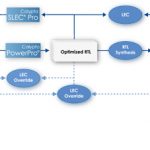

SLEC is Not LEC

One of the questions that Calypto is asked all the time is what is the difference between sequential logical equivalence checking (SLEC) and logical equivalence checking (LEC).

LEC is the type of equivalence checking that has been around for 20 years, although like all EDA technologies gradually getting more powerful. LEC is … Read More