Transistor-level circuit designers have long used SPICE for circuit simulation, mostly because it is silicon accurate and helps them to predict the function, timing, power, waveforms, slopes and delays in a cell before fabrication. RTL designers use digital simulators that have a huge capacity but are lacking analog modeling.… Read More

Tag: jaeha kim

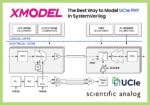

WEBINAR: UCIe PHY Modeling and Simulation with XMODEL

Join this webinar and see UCIe in action! This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog,… Read More

Variation-Aware Custom IC Design Best Practices

I’ve worked with Solido for 5 years, and it’s been a pleasure to watch the world’s top semiconductor companies and foundries adopt Solido software for their SPICE simulation flows.

Sub-28nm design starts are accelerating, growing from 150 in 2012 to 900 this year. The move to sub-28nm design nodes is being driven by consumer electronic… Read More